# 3D-Stacked SPAD in 40/45nm BSI Technology

Shaping the world with sensor solutions

Georg Röhrer June 8, 2020

### **Outline of Presentation**

Motivation for 3D-Stacking Test structure and SPAD description Characterization Results Benchmark

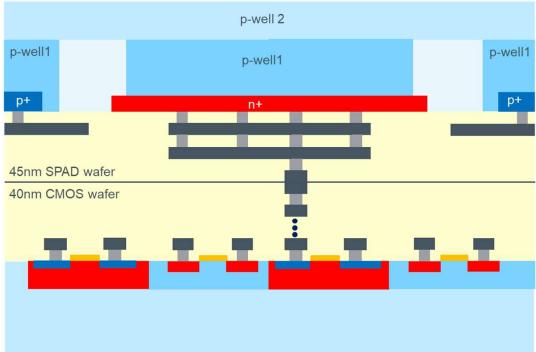

# Motivation for 3D Stacking

- Back side illuminated (BSI)

- Fill factor limited by SPAD only.

- Process for SPAD wafer can be optimized for SPAD performance (e.g. depletion layer width).

- SPAD process can be re-used for different CMOS nodes – enabling optimized products in terms of performance and cost.

## Test Structure and SPAD Schematic

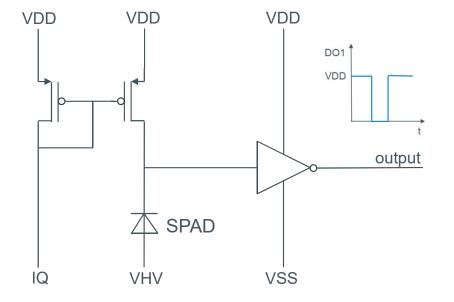

- SPAD is biased between VDD and VHV (negative).

- Passive quenching used.

- Current IQ used to set the dead time over a wide range (~10ns....~10µs).

- For crosstalk characterization, outputs for two neighboring SPADs are available.

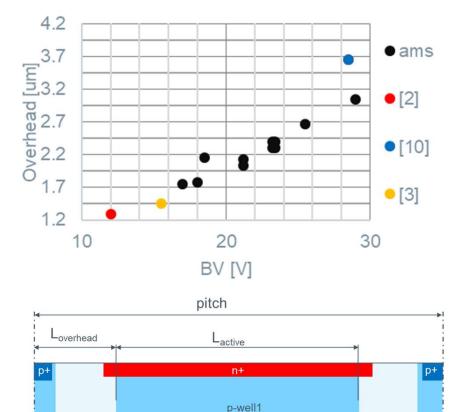

| Fill Factor[%] | L <sub>overhead</sub> [um]       |

|----------------|----------------------------------|

| 25             | 3.15                             |

| 32             | 2.75                             |

| 36             | 2.55                             |

| 40             | 2.35                             |

| 44             | 2.15                             |

| 48             | 1.95                             |

| 52             | 1.75                             |

|                | 25<br>32<br>36<br>40<br>44<br>48 |

Breakdown Voltage

Confidential © ams AG

Page 5

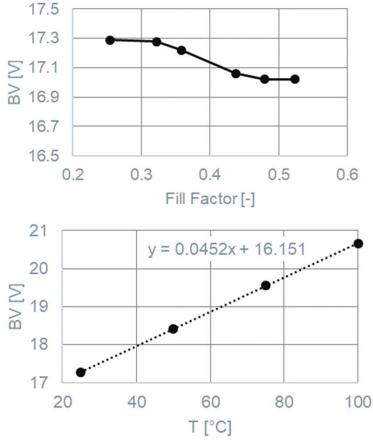

Main impact factors of breakdown voltage:

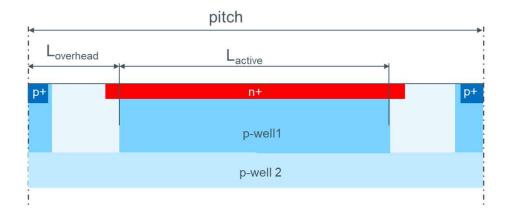

- Achievable fill factor limited by break down voltage. Required minimum "overhead" region scales approximately linearly with breakdown voltage.

- Depletion layer width (impact on PDE, junction capacitance)

- DCR (for low BV, tunneling dominates DCR).

- Energy per SPAD event scales with breakdown voltage.

p-well 2

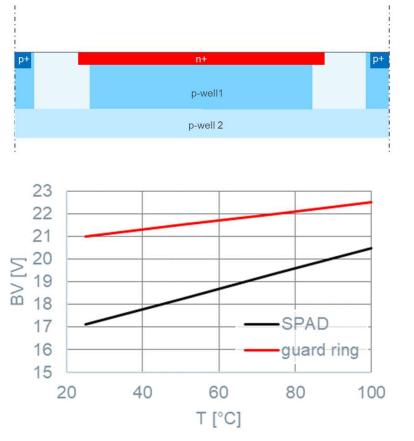

# Breakdown Voltage (VBD)

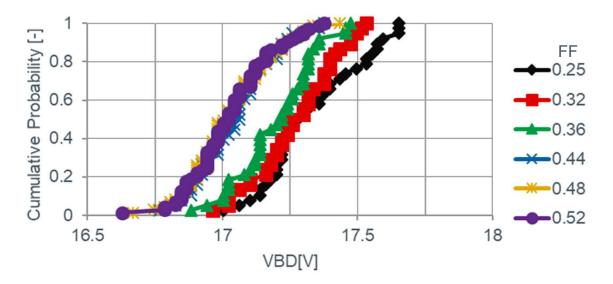

#### **Results for different fill factors**

- VBD slightly decreases with fill factor (250mV).

- Standard deviation of within wafer distribution is ~150mV.

- VBD temperature coefficient is 45mV/°C, no impact of the fill factor.

Confidential © ams AG Page 6

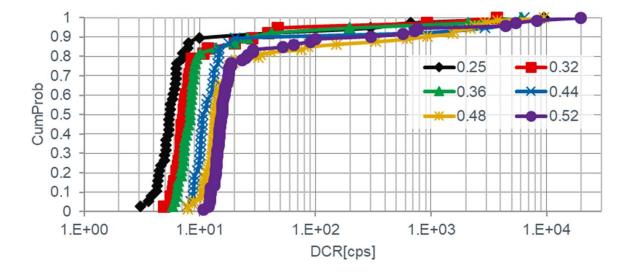

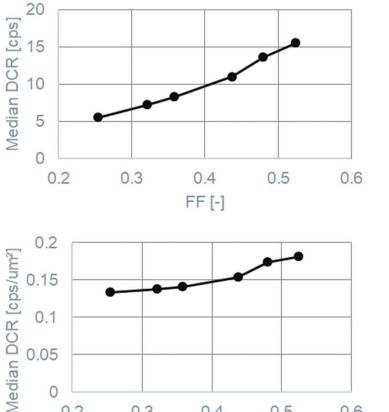

### **Dark Count Rate** 25°C, Vexc=2.0V

0.4

FF [-]

0

0.2

0.3

- DCR (median) is 6cps for a fill factor of 25% and 16cps for a drawn fill factor of 52%.

- Around 80% of SPADs show a DCR close to median value.

- When DCR is normalized to drawn active area, DCR (in cps/um<sup>2</sup>) still increases with fill factor. Indication that drawn active area  $\neq$  real active area.

0.6

0.5

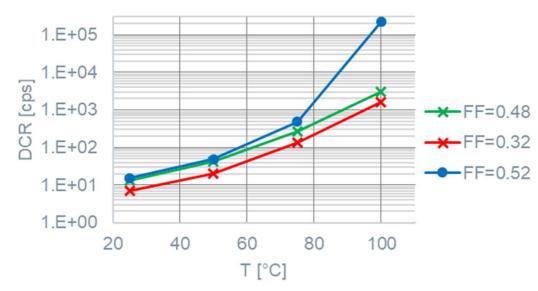

### Dark Count Rate: Temperature Impact Vexc=2.0V

- Activation energy (extracted from 75°C and 100°C measurements) is 1.08eV.

- For the device with the fill factor of 52%, the DCR becomes very high at 100°C, caused by the different temperature coefficient of the guard ring versus the avalanche junction.

Confidential © ams AG Page 8

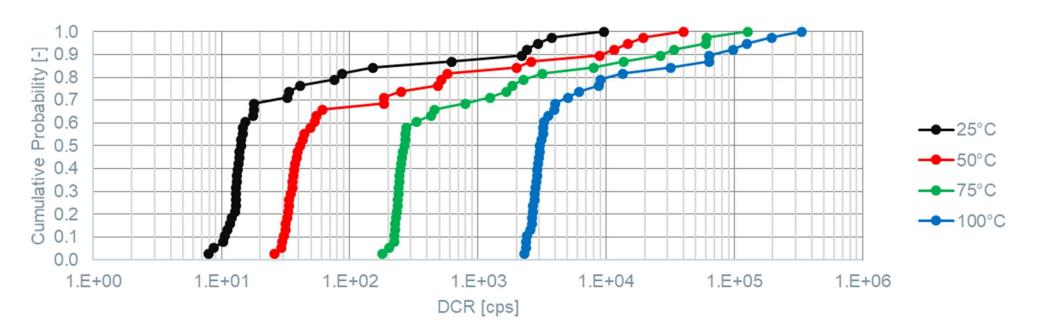

### DCR Distribution for 25/50/75/100°C FF=0.48, Vexc=2.0V

At 75°C, median DCR is 270cps and the most noisy SPAD has a DCR of 130kcps. This is still a reasonable DCR at 75°C!

> Confidential © ams AG Page 9

# Activation Energy for Hot Pixels

1.2 4E+005 1E+005 1 4E+004 0.8 DCR [cps] 0.0 6.0 6.0 8.0 1E+004 4E+003 1E+003 0.4 4E+002 0.2 1E+002 4E+001 0 1.E+03 1.E+04 1.E+05 1.E+06 1E+001 DCR@100°C [cps] 2.65E-003 2.90E-003 3.15E-003 1/T [1/K]

75°C

100°C

50°C

- DCR for 25°C, 50°C dominated by tunneling, for 75°C and 100°C by thermal diffusion.

- Noisy SPADs dominated by diffusion for all temperatures (25°C-100°C).

- Some SPADs are in the main population at 25°C, but end up as hot pixel at 100°C and vice versa.

- Activation energy tends to be lower for SPADs with larger DCR.

Confidential © ams AG Page 10

25°C

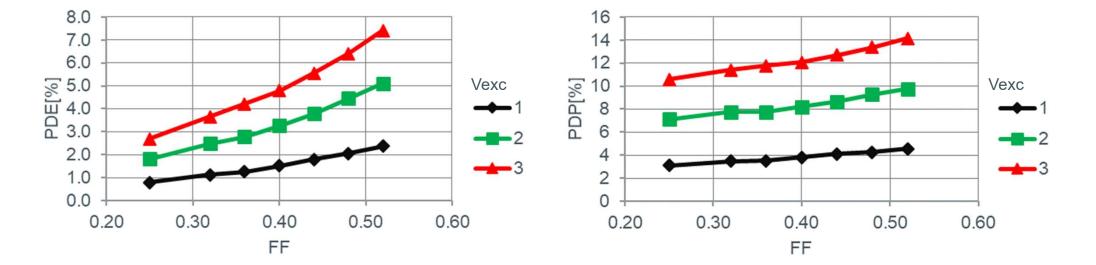

# Impact of Fill Factor on PDE and PDP 940nm

- PDE = PDP \* FF

- PDE increases non-linearly with fill factor.

- Hence PDP is not constant over fill factor.

Confidential © ams AG Page 11

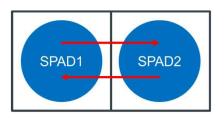

### Crosstalk

**Measurement Method**

Light emission of SPAD1 (when triggered by DCR or light) can trigger the neighboring SPAD2 (or vice versa)  $\rightarrow$ optical orthogonal cross-talk.

The cross talk between SPAD1 and SPAD2 is measured by counting the events for SPAD1, SPAD2 and both SPADs combined. Cross talk is calculated as: (C1+C2-C)/C

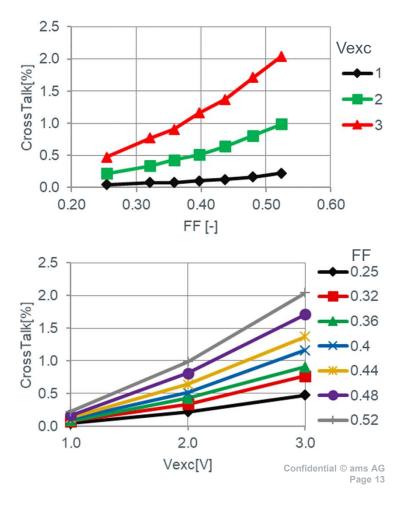

# Impact of Fill Factor and Vexc on Crosstalk (1)

Cross talk increases with fill factor and excess bias voltage.

#### Fill factor:

- Distance between SPAD active area becomes smaller for larger fill factors.

- Capacitance increases with fill factor, thus the charge per SPAD trigger event is increased (more light emission).

- PDE increases with fill factor.

#### **Excess bias voltage:**

- PDE increases ~linearly with excess bias voltage. Thus probability of SPAD triggering is increased.

- The charge per SPAD trigger event increases with excess bias voltage (more light emission).

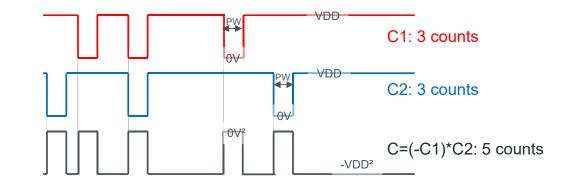

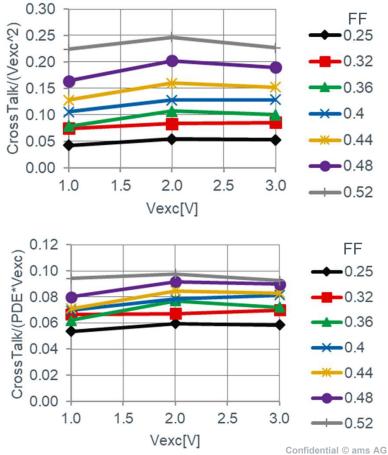

## Impact of Fill Factor and Vexc on Crosstalk (2)

FF

-0.25

-0.32

0.44

-0.48

×−0.4

CrossTalk

$V_{exc} \cdot V_{exc}$

CrossTalk

$V_{exc} \cdot PDE$

2.50

2.00

1.50

.00

0.50

0.00

1.0

1.5

CrossTalk[%]

Excess bias voltage impact nearly eliminated (less then 10% variation over Vexc remains).

3.0

2.5

2.0

Vexc[V]

- Normalization with V<sub>exc</sub><sup>2</sup>: Remaining impact of the fill factor is much stronger, since increase of PDE with fill factor is not taken into account.

- Normalization with V<sub>exc</sub>·PDE: Remaining impact of fill factor due to reduced spacing with fill factor and increased capacitance.

Page 14

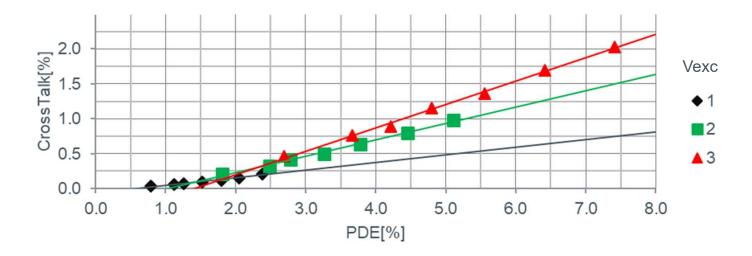

### Crosstalk – PDE Trade-Off

- Trade-off between PDE (@940nm) and cross-talk.

- Slightly worse trade off for larger excess bias voltage.

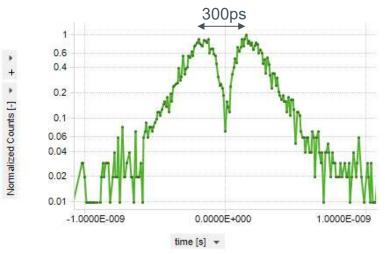

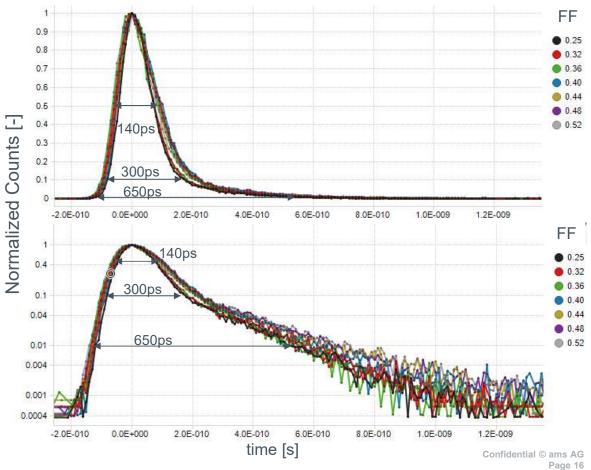

### Timing Jitter @940nm 25°C, Vexc=2.0V, 940nm

| FF   | FWHM | FW@10% | FW@1% |

|------|------|--------|-------|

| 0.25 | 120  | 260    | 630   |

| 0.32 | 130  | 270    | 650   |

| 0.36 | 140  | 290    | 640   |

| 0.40 | 150  | 320    | 680   |

| 0.44 | 140  | 310    | 660   |

| 0.48 | 145  | 310    | 790   |

| 0.52 | 140  | 300    | 830   |

• Good jitter characteristics at 940nm!

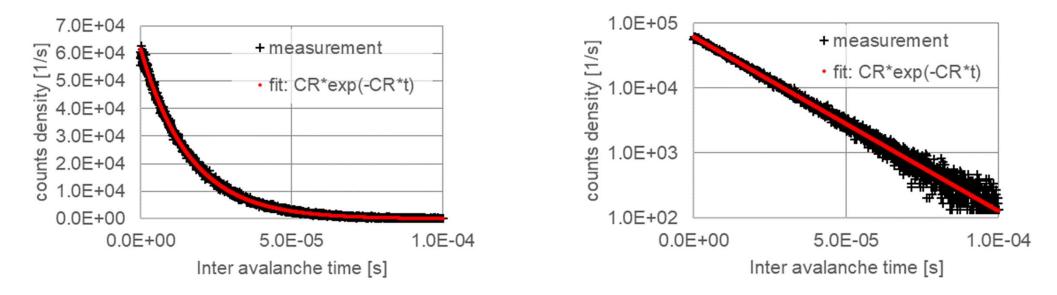

# After Pulsing Probability 25°C, Vexc=3.0V

- After pulsing probability is measured by the inter-avalanche time method.

- Measurement taken with 7ns dead time and low light condition.

- After pulsing probability < 0.5%

## Performance Table

#### Typical parameters at 2V excess bias voltage, FF=0.48

| Key Performance Indicator                  | Unit | Stacked BSI 45/40nm |

|--------------------------------------------|------|---------------------|

| Pixel pitch                                | um   | ~12.5               |

| Breakdown voltage                          | V    | 17.0                |

| DCR (25°C)                                 | cps  | 14                  |

| DCR (75°C)                                 | cps  | 270                 |

| PDE at 940nm                               | %    | 4.5                 |

| Timing jitter FWHM at 940nm                | ps   | 145                 |

| Timing jitter (FW10%M) at 940nm            | ps   | 310                 |

| Timing jitter (FW1%M) at 940nm             | ps   | 790                 |

| After pulsing probability at 7ns dead time | %    | <0.5                |

| Cross talk probability                     | %    | 0.8                 |

Sensing is life.

dr

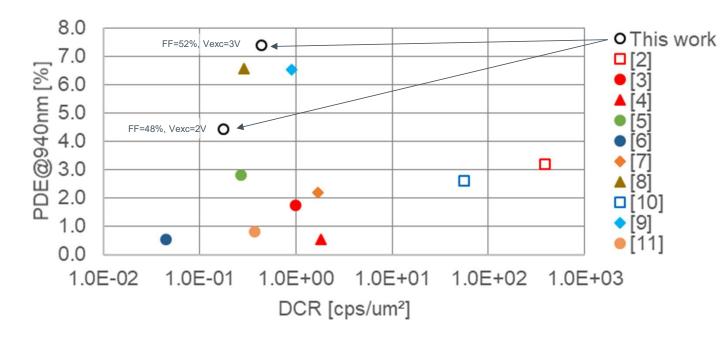

### Benchmark

#### [1] This work

[2] S. Lindner et al., "A High-PDE, Backside-Illuminated SPAD in 65/40-nm 3D IC CMOS Pixel With Cascoded Passive Quenching and Active Recharge", IEEE EDL vol. 38, no. 11, November 2017

[3] S. Pellegrini et al., "Industrialized SPAD in 40nm Technology", IEDM 2017

[4] S. Pellegrini et al., "Fully industrialized single photon avalanche diodes", SPIE proceedings vol. 10212, May 2017

[5] I. Takai et. al, "Single-Photon Avalanche Diode with Enhanced NIR-Sensitivity for Automotive LIDAR Systems", Sensors 16, no. 4: 459

[6] D. Bronzi, "Low-noise and large-area CMOS SPADs with timing response free from slow tails", ESSDERC 2012

[7] A. Fenigstein, "CMOS 0.18um SPAD", ISSW 2018

[8] A. Gulinatti et al., "Improving the performance of silicon

single-photon avalanche diodes", SPIE proceedings vol. 803302, May 2011

[9] A. Gola, "NUV-HD and NIR-HD SiPMs and Applications", ISSW 2018

[10] M. Lee et al., "High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-nm CMOS Technology", IEEE Journal of Selected Topics in Quantum Electronics, vol. 24, issue 6, Nov.-Dec. 2018

[11] M. Morimoto et al., "High fill-factor miniaturized SPAD arrays with a guard-ring-sharing technique", Optics Express, vol. 28, issue 9, 2020

# Thank you!

Please visit our website www.ams.com