# 3μm Pitch, 1μm Active Diameter SPAD Arrays in 130nm CMOS Imaging Technology

Ziyang You<sup>1</sup>, Luca Parmesan<sup>1\*</sup>, Sara Pellegrini<sup>2</sup>, Robert K. Henderson<sup>1</sup>

1 CMOS Sensors and Systems Group, School of Engineering, The University of Edinburgh, UK, EH9 3JF, Robert.Henderson@ed.ac.uk

2 STMicroelectronics, Imaging Division, Tanfield, Edinburgh, UK, EH3 5DA. \*now with Fondazione Bruno Kessler, Trento, Italy

Abstract— A shared well 4x4 SPAD array test structure with 3μm pitch is realized in a 130nm CMOS image sensor technology. The SPADs have 150Hz median DCR at room temperature at 1V excess bias, 15% peak PDP and 176ps FWHM timing jitter both at 3V excess bias.

*Index Terms*— Single photon avalanche diode, photon counting, CMOS image sensor.

## I. INTRODUCTION

CMOS Single Photon Avalanche Diode (SPAD) imaging arrays implemented with advanced CMOS process nodes, 3D-hybrid bonding and backside-illumination (BSI) offer a pathway towards digital photon counting cameras with high sensitivity, temporal resolution and dynamic range [1]. Such technologies solve the severe trade-off implicit in front-side illuminated (FSI) SPAD imagers between fill-factor and pixel functionality which are being addressed by analogue pixel techniques, shared-pixel layouts, microlenses and high temporal oversampling [2][3][4][5]. The advent of hybrid Cu-Cu direct bonding offers per-pixel connection between a dense SPAD-only top-tier with a photon counting, timing and readout matrix in the bottom-tier, decoupling the individual scaling challenges of detector, hybrid-bond and electronics towards small pixel pitches.

SPADs with active diameters as low as 2µm have been investigated either as isolated test structures or in shared well arrays with source follower buffers at 5µm pitch [6][7][8][9]. Recent reports of shared-well SPAD imagers at 7.83µm and 8.25µm pitch with fill-factors in excess of 50% point the way towards pixel pitches compatible with high-resolution imaging [1][10]. Apart from the loss of fill-factor, this scaling is attractive for many SPAD properties such as timing jitter, dark count rate and crosstalk which are improved as the detector volume and avalanche charge reduce [6]. A hybrid pixel combining Geiger-mode avalanche multiplication with a pinned-photodiode was recently proposed through modulation of a high voltage back-bias [11]. The 3.8 µm pitch 1Mpix BSI imager exhibits 100dB dynamic range and very low dark count. However, the avalanche mode operates without harnessing the photon counting and timing properties available from SPAD pixels.

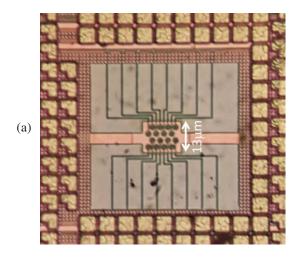

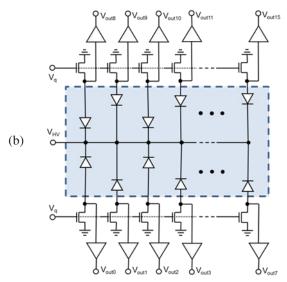

Fig. 1. 4 x 4 shared well SPAD array with individually accessible anodes (a) layout (b) circuit schematic.

In this paper we demonstrate the smallest pitch SPAD array in the literature suited to implementing future high resolution stacked SPAD imagers. Although the structure is implemented in a 130nm 4LM FSI CMOS image sensor technology, it could act as the top-tier BSI SPAD layer in a stacked imager by being inverted and ported to a BSI technology [1]. Section II describes the device structure, Section III the device measurements while Section IV discusses future perspectives for imaging arrays.

#### II. SPAD TEST STRUCTURE DESCRIPTION

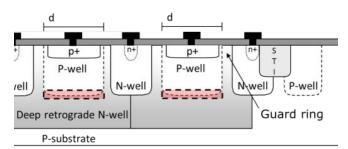

Fig. 2. Cross section through two SPADs sharing a common deep n-well cathode and the periphery of the array

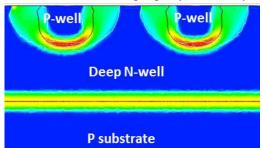

Fig. 3. TCAD electric field plot showing two multiplication regions (red) and low field guard rings (green)

The 3 µm pitch 4 x 4 test structure (Fig. 1a) employs a scalable 1 µm diameter SPAD structure [6]. The SPADs are arranged in a honeycomb style to maximize fill-factor achieving around 14%. All anodes of the 4 x 4 structure are wired individually to NMOS quench circuits and buffers placed a few microns away from the periphery of the shared well (Fig. 1b). A 16x16 silicon photomultiplier array of these devices has also been integrated and is the largest achievable without occluding the anodes with the 3 metal routing layers. Fig. 2 shows the device cross-section consisting of a p-well to retrograde deep n-well avalanche region and a virtual guard ring. Shared well arrays of this SPAD structure have been implemented at large pixel pitches and fill-factors in digital silicon photomultipliers [12], however never before at this extremely small dimension. TCAD simulation is used to confirm that the high field breakdown region is confined below the p-well and that a reduced field in the periphery acts as an effective guard ring (Fig. 3).

## III. MEASUREMENT RESULTS

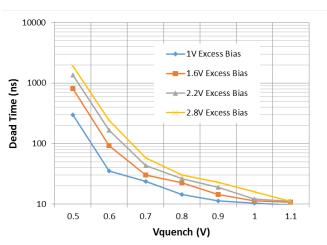

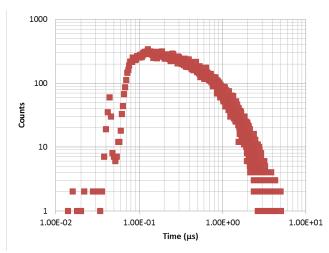

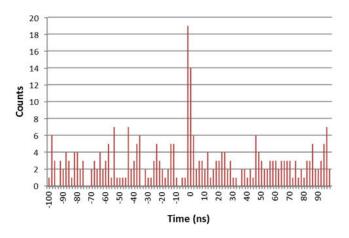

The breakdown voltage of the SPADs is 15.8V. A median dark count rate (DCR) of 150Hz is measured at 1V excess bias and room temperature. Fig. 4 shows a minimum dead time of 10ns limited by buffer drive strength and pad capacitive loading. Fig. 5 shows a 100k event inter-arrival time histogram of a SPAD biased at 1V excess bias operating with a dead time of 10ns. The region below 50ns shows an increase of pulse rate beyond the Poisson curve indicating an afterpulsing rate of 0.18%. Optical crosstalk is characterized by generating a histogram of the inter-arrival times ( $t_{\rm diff}$ ) of two devices revealing an uncorrelated noise floor and a sharp peak of a few 100ps FWHM around  $t_{\rm diff}$ =0 (Fig. 6).

Fig. 4. SPAD dead time as a function of NMOS quench gate voltage.

Fig. 5. Inter-arrival times of a SPAD operating at 1V excess bias and 10ns dead time.

Fig. 6. Zoomed histogram of inter-arrival times of two different SPADs used to study optical crosstalk (15k events)

We count pulses in a region of +/-2ns around  $t_{\rm diff}$ =0s to perform our crosstalk calculation. This allows crosstalk to be studied in ambient conditions reducing acquisition times, and without the need to enable or disable device anodes [13].

Fig. 7. Crosstalk map of the SPAD array at 1V excess bias.

Crosstalk is then calculated by integrating counts in the peak, compensated for the ambient count rate and dividing by the total number of events. As expected, the crosstalk is much lower (<0.2%) than larger devices and decreases with distance from the emitter (Fig. 7) [13].

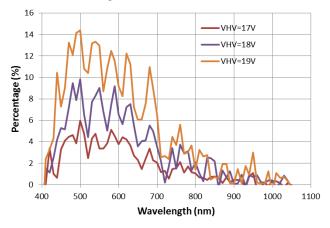

Fig. 8. Photon detection probability plotted against wavelength

Fig. 8 shows the spectral response of the detector. A peak photon detection (PDP) probability of 15% at 500nm is measured at 3.2V excess bias. This is a factor of 2-3x lower than larger diameter realizations of the same device structure [12][13]. The PDP increases linearly at 4%/V with excess bias and shows strong Fabry-Perot interference effects in the front-side 4 metal optical stack.

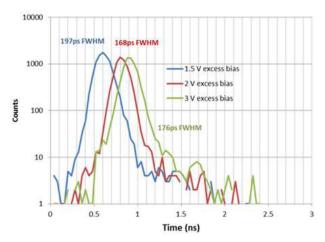

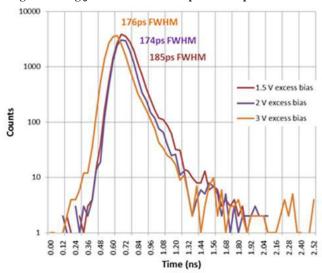

The SPAD timing jitter is plotted in Fig. 9 and Fig. 10. This was measured in response to two wavelengths of Hamamatsu PLP-10 pulsed lasers attenuated by neutral density filters to fraction of a photon per pulse. The timing jitter shows little voltage dependence and marginally higher full-width half maximum (FWHM) at the longer wavelengths. The jitter tail of these devices is short confirming the trend seen in previous measurements of such small devices [6].

Fig. 9. Timing jitter of SPAD in response to a pulsed 445nm

Fig. 10. Timing jitter of SPAD in response to pulsed 773nm laser

## IV. DISCUSSION

The performance of the device is relatively poor compared to the state of the art (Table I). The device exhibits a high DCR per unit area (190Hz/ $\mu$ m2), an increased breakdown voltage, higher timing jitter and a lower PDP compared to larger devices of the same construction [6]. Although measurements of the variation of DCR with temperature and voltage indicate tunneling within the device, this behavior is not predicted by 2D TCAD simulation. More detailed modelling and investigation of the mechanism is being pursued.

Nevertheless, our test structure demonstrates that SPAD devices can be scaled to the small dimensions required for future high resolution quanta-image sensors (QIS). Few micron pitch SPAD arrays can then be employed in hybrid-bonded top tier pitch BSI imagers. This awaits progress in manufacturing of per-pixel hybrid bonds at such dimensions which is a topic of much industry activity. A key research question then arises; how to realize photon counting and timing pixel electronic matrices in the bottom tier at these

small pitches? Two approaches are immediately evident borrowing techniques proposed with limited fill-factor in front-side illuminated realizations. The first is the use of analogue pixels based on either gated photon counting or time to analogue conversion [14]. The second is the design of digital pixels in advanced nanometer process nodes to implement gated counters or time to digital converters [15].

## V. CONCLUSION

A test structure demonstrates that SPAD devices can be scaled to the small dimensions required for future high resolution quanta-image sensors when ported to stacked BSI technologies. Further research into few micron pitch SPAD arrays is required to improve the device performance.

#### ACKNOWLEDGMENTS

The authors gratefully acknowledge support of STMicroelectronics (L. Parmesan Ph.D. funding and manufacture of silicon), the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/K00042X/1 and European Research Council (ERC) under Grant 339747. We are grateful for the assistance of Tarek Al Abbas for characterization and Alexandre Lopez for TCAD simulations.

#### VI. REFERENCES

- [1] T. Al Abbas, N. Dutton, O. Almer, S. Pellegrini, Y. Henrion and R.K. Henderson," Backside Illuminated SPAD Image Sensor with 7.83µm Pitch in 3D-Stacked CMOS Technology", In Proc. IEEE International Electron Devices Meeting, San Francisco, Dec. 2016.

- [2] N.A.W. Dutton, I Gyongy, L. Parmesan, S. Gnecchi, N. Calder, B.R. Rae, S. Pellegrini, L.A. Grant, and R.K. Henderson; "A SPAD-Based QVGA Image Sensor for Single-Photon Counting and Quanta Imaging", IEEE Trans. Electron Devices 2016, 63, 189–196.

- [3] M. Perenzoni, L. Pancheri, and D. Stoppa, "Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors," Sensors, vol. 16, May 2016.

- [4] S. Burri, Y. Maruyama, X. Michalet, F. Regazzoni, C. Bruschini, and E. Charbon, "Architecture and applications of a high resolution gated SPAD image sensor", Opt. Express 2014, 22, 17573–17589.

- [5] J.M. Pavia, M. Wolf, E. Charbon, "Measurement and modeling of microlenses fabricated on single-photon avalanche diode arrays for fill factor recovery", Opt. Express 2014, 22, 4202–4213.

- [6] J.A. Richardson, E.A.G. Webster, L.A. Grant, and R.K. Henderson, "Scalable single-photon avalanche diode structures in nanometer CMOS technology," IEEE Trans. Electron Devices, vol. 58, no. 7, pp. 2028–2035, Jul. 2011.

- [7] E.A.G. Webster, J.A. Richardson, L.A. Grant, and R.K. Henderson, "Single-photon avalanche diodes in 90 nm CMOS imaging technology with sub-1 Hz median dark count rate," in Proc. Int. Image Sensor Workshop (IISW), 2011, pp. 1–4.

- [8] R.K. Henderson, E.A.G. Webster, R. Walker, J.A. Richardson, and L.A. Grant, "A  $3\times3$ ,  $5\mu m$  pitch, 3-transistor single photon avalanche diode array with integrated 11 V bias generation in 90 nm CMOS technology," in Proc. IEEE IEDM, Dec. 2010, pp. 14.2.1–14.2.4.

- [9] J.A. Richardson et al., "A 2 µm diameter, 9Hz dark count, Single Photon Avalanche Diode in 130nm CMOS technology", Proc. IEEE European Solid-State Device Research Conference (ESSDERC), 2010, pp. 257-260.

- [10] T. Al Abbas, N.A.W. Dutton, O. Almer, F.M. Della Rocca1, S. Pellegrini, B. Rae, D. Golanski and R.K. Henderson, "8.25µm Pitch 66% Fill Factor Global Shared Well SPAD Image Sensor in 40nm CMOS FSI Technology", in Proc. Int. Image Sensor Workshop (IISW), 2017.

- [11] M. Mori;Y. Sakata, M.Usuda, S. Yamahira, S.Kasuga, Y. Hirose, Y. Kato and T.A. Tanaka, "1280  $\times$  720 single-photon-detecting image sensor with 100 dB dynamic range using a sensitivity-boosting technique". In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 120–121.

- [12] L. Braga, L. Gasparini, L. Grant, R. Henderson, N. Massari, M. Perenzoni, D. Stoppa, and R. Walker, "A fully Digital 8x16 SiPM array for PET applications with per-pixel TDCs and real-time energy output," IEEE J. Solid-State Circuits 49, 301–314 (2014).

- [13] H Xu, L Pancheri, L.H.C. Braga, G.F. Dalla Betta, D Stoppa, "Cross-talk characterization of dense single-photon avalanche diode arrays in CMOS 150-nm technology", Optical Engineering 55 (6), 067102-0.

- [14] M. Perenzoni, L. Pancheri, and D. Stoppa, "Compact SPAD-Based Pixel Architectures for Time-Resolved Image Sensors," Sensors, vol. 16, May 2016.

- [15] N.A.W. Dutton, T. Al Abbas, I. Gyongy and R.K. Henderson, "Extending the Dynamic Range of Oversampled Binary SPAD Image Sensors", in Proc. Int. Image Sensor Workshop (IISW), 2017.

|                      | This Work             | [6]                            | [7]                             | [9]                      | [11]                            |

|----------------------|-----------------------|--------------------------------|---------------------------------|--------------------------|---------------------------------|

| Technology           | 130nm                 | 130nm                          | 90nm                            | 90nm                     | 110nm                           |

|                      | CIS                   | CIS                            | CIS                             | CIS                      | BSI                             |

| Diameter (Pitch)     | 1μm                   | 2μm                            | 2μm                             | 2μm                      |                                 |

|                      | (3µm)                 |                                |                                 | (5µm)                    | (3.8 µm)                        |

| Junction/GR          | p-well/p-epi          | p-well/p-epi                   | p-well/p-epi                    | p-plus/n-well            | buried n-p                      |

| structure            |                       |                                |                                 | virtual                  |                                 |

| VBD @RT              | 15.8V                 | 14.4V                          | 17.7V                           | 10.3V                    | 23V                             |

| Median               | 190Hz/μm <sup>2</sup> | $2.9$ Hz/ $\mu$ m <sup>2</sup> | $0.39$ Hz/ $\mu$ m <sup>2</sup> | 79.639Hz/μm <sup>2</sup> | $0.88$ Hz/ $\mu$ m <sup>2</sup> |

| DCR/Area             | @1.2V                 | @1.2V                          | @1.2V                           | @0.6V                    | @2V                             |

| PDP Peak             | 15% @ 3.2V            | 14% @ 1.2V                     | 33% @ 1.2V                      | 36%@0.6V                 | -                               |

| Timing Jitter (FWHM) | 185ps @ 3V            | 136ps @ 1.2V                   | 103ps @ 1.2V                    | 107ps @0.6V              | -                               |

Table I: Few micron diameter SPAD performance comparison