# Linear High-Dynamic-Range Bouncing Pixel with Single Sample

Pablo N. A. Belmonte<sup>1,2</sup>, P.J. French<sup>2</sup>, Davies W. De Lima Monteiro<sup>1</sup>, Frank Sill Torres<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, DEE/PPGEE, Universidade Federal de Minas Gerais, Belo Horizonte, MG, Brazil

<sup>2</sup>Delft University of Technology, Electronic Instrumentation Laboratory, Mekelweg 4, 2628 CD Delft, The Netherlands

Tel: +55 31 3409-3416; email: pablonuneagb@gmail.com, davies@ufmg.br

Abstract—An alternative pixel topology for CMOS image sensors with High Dynamic Range (HDR) is presented. The pixel is based on an approach that allows the HDR sensor to operate with linear response and yet, with just a single sample, and achieve constant sensitivity, apart from noise effects, throughout the whole DR. The control is simple, automatic and on pixel, always yielding HDR images with no complex embedded algorithms or image post processing. The pixel was simulated in a 0.35  $\mu$ m standard CMOS technology, achieving a DR of up to 118dB. Pixel architecture and detailed operation are discussed, and simulation results are presented.

Index Terms—Dynamic range (DR), CMOS image sensors, linear response, sensitivity

#### I. INTRODUCTION

ONE OF THE key requirements for many imaging applications is high sensitivity as well as High Dynamic Range (HDR). The latter is defined as the ratio between the brightest and the darkest resolvable points or regions on an image. While the feature size in CMOS technology continuously downscales, enabling high resolution imaging, usually limited by the camera lens, they also affect negatively the DR and sensitivity, by means of the increased leakage current, noise components, limited quantum efficiency and reduced signal swing [1]. Dealing with these issues and designing HDR sensors while keeping good sensitivity is not a straightforward task.

Regarding this matter, many solutions for HDR image sensors have been proposed. Generally, they are classified into seven different categories [2]: 1) The Companding sensors, or logarithm sensors, have a very simple control and high DR, but with signal non-linearity and poor sensitivity at high illumination levels, resulting in lower modulation transfer function over a scene [3]; 2) Multimode sensors operate in both logarithm and linear modes [4,5], achieving very high DR, while increasing sensitivity for lower illumination levels. However, they still have poor sensitivity at high light intensities, while demanding a more sophisticated control, and non-trivial signal processing; 3) Clipping sensors [6,7] use

Capacitance Adjustment, which combines the response of different capacitances, i.e. different sensitivities, in order to achieve a HDR, which renders the control and signal processing more complex; 4) Frequency-based sensors [8,9] have linear response, while achieving HDR with a high frame rate. However, they have lower sensitivity to low illumination levels, since they just detect saturation events; 5) Time to firstspike (TTS) sensors [10,11] have very high DR, and high frame rate as well, but still suffer under low sensitivity at high illumination levels. Further, they need very precise time controlling and high resolution of the saturation time representation; 6) Global-control-over-the-integration-time sensors [12,13] and 7) Autonomous-control-over-theintegration-time sensors [14,15] implement multiple capture algorithms, which require complex signal processing and control, without solving the problem of the sensitivity at highlights. Besides that, they have lower frame rate due to the need of multiple exposures.

For the usual HDR approaches, the main drawbacks are poor sensitivity at higher or lower illumination levels, nonlinear response, reduced frame rate (multiple captures required), sophisticated control and non-trivial image processing. The pixel that seems to fulfill all these requirements is the conventional linear APS (Active Pixel Sensor) topology which however features very low DR. If it was possible to increase the voltage swing to a very large extent, for a fixed integration time ( $\Delta T$ ), the aforementioned issues would be solved, since the response would be linear, a single capture would be needed, and  $\Delta T$  would not need to be shortened for high illumination levels, which seriously affects the sensitivity. But, the usually low chip supply voltage in standard CMOS processes precludes any considerable increase in the voltage swing.

However, the increase of the voltage swing can be emulated. For this purpose we have envisioned a pixel-circuit topology, based on the Current-Mirroring-Integration (CMI) architecture [16,17,18], which yields a very high DR within a pre-set integration time in the reset-integration cycle, with linear response, single sample, and constant sensitivity.

This work has been supported by the Brazilian agency CAPES, Fundação de Pesquisa do Estado de Minas Gerais - FAPEMIG and Conselho Nacional de Pesquisa - CNPq and has also been realized in the scope of INCT-DISSE.

# A. Principle of Operation

In order to reconstruct an image, voltage-mode CMOS image sensors must provide information about both time and voltage for each pixel. Usual solutions for HDR are to alter the integration time for different pixels in the same frame, keeping the voltage swing constant, or accommodate the signal in a constant voltage and time interval. What is not normally done is try to enhance the voltage swing [16,19] conserving a constant integration time.

The CMI topology uses a feedback structure based on current mirrors, featuring stable bias voltage across the photodetector and low input impedance, while mirroring the photogenerated current to an integration capacitor. As the current is integrated, the voltage increases over the integration time with a slope proportional to the pixel photocurrent.

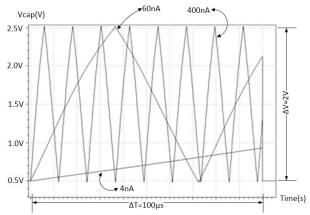

The main idea of the circuit is to prevent that the integrated voltage reaches saturation; instead, the signal bounces at a reference upper signal and continues to integrate downwards, maintaining the slope, until it eventually reaches the lower reference limit and re-bounces upwards. This process repeats itself every time the signal would saturate within the boundaries of a stipulated voltage difference. Figure 1 illustrates the concept for different photocurrent values. The number of bounces is then counted and the output comprises two signals: a digital one, indicating the number of bounces; and an analog one, i.e. the voltage of an off-pixel capacitor  $(V_{CAP})$ . With these two signals a high DR can be achieved.

Fig. 1. Integrated Output Voltage across the capacitor for three different

The dynamic range extension factor (DRF) [2] is calculated as follows:

$$DRF = 20\log\left(\frac{I_N}{I_1}\right) = 20\log(N) \tag{1}$$

$$DRF = 20 \log \left(\frac{l_N}{l_1}\right) = 20 \log(N)$$

(1)

$$I_k = \frac{C \cdot (\Delta V \cdot k)}{\Delta T} , k = 1, 2 \dots N$$

(2)

where C is the value of the off-pixel integration capacitor,  $\Delta V$ the stipulated voltage difference,  $\Delta T$  the pre-set integration time, and k is the emulated voltage-increase factor (i.e. the number of counted bounces);  $I_k$  is the photocurrent when the

$k^{\text{th}}$  bounce occurs, and  $N = 2^b$  is the maximum number of rebounces, for a b-bits counter;  $I_N$  represents the largest photocurrent measurable before the counter reaches saturation, and  $I_1$  the photocurrent when the first bounce occurs. Hence, the DRF depends on the counter size b. For an 8-bit counter the DRF exceeds 48dB. The DRF measures how much the DR can be extended. For instance, for the normal pixel, without re-bouncing, with a DR<sub>0</sub> equal to 60dB, the maximum photocurrent before saturation will be  $I_1$ . So, for the bouncing pixel, the new DR<sub>N</sub> will be:

$$DR_N = 20 \log \left(\frac{I_N}{I_{min}}\right) = 20 \log \left(\frac{I_1}{I_{min}} \cdot \frac{I_N}{I_1}\right) = DR_0 + DRF$$

(3) where  $I_{min}$  is the minimum photocurrent. The above equation yields a DR<sub>N</sub>=108dB.

To reconstruct the image, one must combine the analog and the digital values for each pixel. The analog one is the offpixel capacitor voltage  $(V_{CAP})$  and is read as usual at the end of  $\Delta T$ . The digital one is the number of bounces (k) that were counted. Then, the final reconstructed value  $(V_R)$  is:

$$V_R = \Delta V \cdot k + V_{CAP} \tag{4}$$

for *k* even, or:

$$V_R = \Delta V \cdot (k+1) - V_{CAP} \tag{5}$$

for k odd.

For a given photocurrent  $i_{ph}$ , let  $t_{up}$  be the time spent by the signal to go from the bottom to the top of the voltage difference  $\Delta V$ , and  $t_{down}$  the time spent to go downwards. If the slope does not vary, meaning the photocurrent is constant, which we assume here, then:

$$t_{up} = t_{down} = t_1 \tag{6}$$

Likewise, let  $t_2$  be the time spent from the last re-bounce ( $k^{th}$ ) to the end of the integration time  $\Delta T$ . If no bounces occurs, then  $t_2 = \Delta T$ , and  $t_1 = 0$ . We can rewrite (4) as:

$$V_R = \left(\frac{i_{ph}}{C} \cdot t_1\right) k + \frac{i_{ph}}{C} \cdot t_2 \to V_R = \frac{i_{ph}}{C} \Delta T \tag{7}$$

since  $\Delta T = t_1 \cdot k + t_2$ . In a similar way, it can be demonstrated that (7) is also true for k odd. According to this equation, the relation between  $V_R$  and  $i_{ph}$  is linear.

Regarding optimal sensitivity, i.e. disconsidering noise effects, one can calculate it by the following equation [2], using the relation in (7):

$$S = \frac{dV_R}{di_{ph}} = \frac{d}{di_{ph}} \left( \frac{i_{ph}}{c} \Delta T \right) = \frac{\Delta T}{c}$$

(8)

The above equation yields the remarkable fact that the sensitivity is constant throughout the whole DR, as long as  $\Delta T$ and C are kept constant. Equations (7) and (8) are identical to those derived for the conventional APS topology in [2].

### B. Pixel Architecture and Analysis

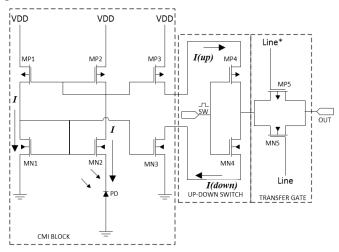

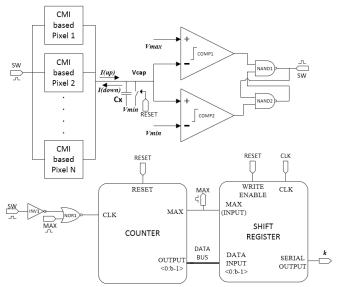

The unit cell (Figure 2) is composed of a few transistors based on the CMI topology. Further, the off-pixel components are shared by all pixels of one, or more, columns of an imager. These shared components consist of a comparison unit, a counter, a shift register and an integration capacitance, as seen in Figure 3.

The CMI pixel topology simplifies the internal and automatic control of the pixel, allowing the external control of the matrix to be very simple and conventional. It just needs two signals: the reset, for the pixels; and the clock, for the digital circuit of each column. Both of them are global, and the integration period  $\Delta T$ , controlled by the reset, can be kept fixed, obtaining constant sensitivity throughout the full illumination range, as reported earlier. If needed, the integration time can be easily modified, preserving the same DRF, but modifying sensitivity and DR. Generally, for a constant C, shrinking  $\Delta T$  will increase DR, and decrease sensitivity (and vice-versa). So, there must be a compromise. The circuit also needs a control signal for each cell on a row, the select signal (Line), which enables the output of each pixel.

Fig. 2. CMI based pixel

Circuit operation: the photocurrent generated by the photodiode PD passes through MN2 and is mirrored to MN1 by the current mirror formed by MP1-MP2. But, since MN1 and MN2 are also connected as current mirrors, their gate-tosource voltage are forced to be the same, resulting in an almost-zero detector bias. To apply a stable non-zero bias through the PD, one must simply substitute the source connection of MN1 to a DC supply, instead of connecting it to the ground. Furthermore, this structure also results in low input impedance. Hence, most of the photocurrent generated by the PD is injected into the circuitry, even when the detector has low resistance. Transistors MN3 and MP3 are responsible for copying the photocurrent to the "up-down switch" formed by MN4-MP4. Basically, this switch selects which current will be delivered to the output through using the transfer gate (MN5-MP5). Both photocurrents have the same absolute value, but they are in opposite directions. When the digital

internal control signal SW is low, then the current I(up) copied by MP3 passes to the output of the unit cell, and is integrated by the off-pixel capacitor Cx, shown in Figure 3. When the voltage  $V_{\rm cap}$  on the capacitor reaches the upper reference  $V_{\rm max}$ , the first comparator sends a signal to the latch (NAND1-NAND2), which generates automatically the signal SW. That will be now high, and the "up-down switch" will now allow the current I(down) mirrored by MN3 to flow. Further, the capacitor will start to discharge until its voltage  $V_{\rm cap}$  reaches the bottom reference  $V_{\rm min}$ , which sets SW to low again. This process repeats itself until the end of the integration period, defined by the signal RESET.

When the RESET signal is low, then the integration time starts, and during this period the counter will count at every edge of SW, i.e. every time the signal  $V_{\rm cap}$  reaches the top or the bottom reference. The two logic gates (INV1 and NOR1) between SW and the input clock of the counter is just to make sure that the counter will stop to count, after the last rebounce (when MAX is set to high). The counted value is then transferred to the Shift Register, which will write it out when RESET goes from low to high.

Fig. 3. One (or more) Column shared circuit.

In fact, the Shift Register has b+1 bits, in order to read also the MAX bit, otherwise information of whether the pixel saturated or not would be lost, and would not have any difference in the final value between a very high photocurrent and a very low. After writing the counter value in its internal registers, the Shift Register starts to shift its value to the serial output at every cycle of clock (CLK). At the beginning it sends a start signal, composed by a binary 10, after that, it delivers the MAX bit followed by the other b bits. Before the end of the high period of the RESET, which has to be large enough to allow all bits to be transferred, the  $V_{\rm cap}$  value must be read, and the pixel operation is completed. As all pixels in one or more columns share the same components, the imager operates in rolling shutter mode.

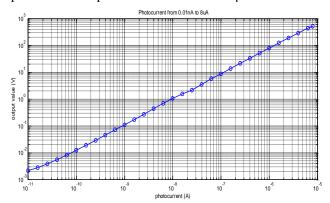

As said before, the circuit has a linear response as can be seen in Figure 4, with photocurrents varying from 10pA to

8μA. This leads to a high DR reaching 118dB.The chosen parameters of the depicted example are: b=8,  $V_{min}$ =0.5V,  $V_{max}$ =2.5V, and  $V_{DD}$ =3.3V. The voltage difference  $\Delta V$ = $V_{max}$ - $V_{min}$  is arbitrary. Increasing it, results in higher DR, but can also lead the capacitor to operate in a slightly nonlinear region, affecting the final response, so there must be a compromise. The capacitance used was C = 1pF.

Fig. 4. Linear response through DR, from 10pA to  $8\mu A$ , leading to DR=118dB. The output value in the y-axis is equal to  $V_R$ .

The response of figure 4 is the raw data extracted by the arithmetic equation described by (4) and (5). It is possible to render its linearity even better with some additional software corrections, but it is not the purpose of this work. Furthermore, the output value  $V_R$  in Figure 4 is not the actual voltage across the capacitor, but the one that would have corresponded to full current integration if re-bouncing was not done and the supply voltage was not limited.

## III. CONCLUSION

In the present work, we have introduced an alternative approach for HDR image sensors. The bouncing pixel does not seem to fit in any of the seven categories presented in [2]. Simulations of the proposed pixel topology, designed in the AMS CMOS 0.35µm technology were presented to validate the concept. The pixel has constant sensitivity throughout the full illumination range, and at the same time, achieves a high DR of 118dB with just a single sample, making it possible to reach higher frame rates, and providing a linear response, allowing a homogeneous contrast reproduction over a scene. Moreover, the whole process to obtain the output value, and thus, the final processed image, can be automatically done, with no need of additional line control, nor any user input, achieving an always-on HDR image.

The pixel layout was already designed, and sent to fabrication. Further improvements and practical results will be presented in future work.

#### REFERENCES

- O. Yadid-Pecht and R. Etienne-Cummings, CMOS Imagers: From Phototransduction to Image Processing. Norwell, MA: Kluwer, 2004.

- [2] A. Spivak, a. Belenky, A. Fish, O. Yadid-Pecht, "Wide Dynamic Range CMOS Image Sensors – Comparative Performance Analysis", IEEE Transactions on Electron Devices, 2009, Vol. 56, Issue 11, pp. 2445-2461

- [3] Y. Hagihara, "Logarithmic-converting CMOS area image sensors with an FPN cancel circuit," in *Japanese*, Eizou Jouhou Media Gakkai Publication(Image Information Media Society), vol.55, no.7, 1039-1044, 2001.

- [4] N. Akahane, R. Ryuzaki, S. Adachi, K. Mizobuchi, and S. Sugawa, "A 200 dB dynamic range iris-less CMOS image sensor with lateral overflow integration capacitor using hybrid voltage and current readout operation," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2006, pp. 1161–1170

- [5] C. E. Fox, J. Hynecek, and D. R. Dykaar, "Wide-dynamic-range pixel with combined linear and logarithmic response and increased signal swing," Proc. SPIE, vol. 3965, pp. 4–10, May 2000

- [6] S.Decker, D. McGrath, K. Brehmer, and C. G. Sodini, "A 256 × 256 CMOS imaging array with wide dynamic range pixels and columnparallel digital output," IEEE J. Solid-State Circuits, vol. 33, no. 12, pp. 2081–2091, Dec. 1998.

- [7] N. Akahane, S. Sugawa, S. Adachi, K. Mori, T. Ishiuchi, and K. Mizobuchi, "A sensitivity and linearity improvement of a 100-dB dynamic range CMOS image sensor using a lateral overflow integration capacitor," IEEE J. Solid-State Circuits, vol. 41, no. 4, pp. 851–858, Apr. 2006.

- [8] X. Wang, W. Wong, and R. Hornsey, "A high dynamic range CMOS image sensor with inpixel light-to-frequency conversion," IEEE Trans. Electron Devices, vol. 53, no. 12, pp. 2988–2992, Dec. 2006.

- [9] K. P. Frohmader, "A novel MOS compatible light intensity-to-frequency converter suited for monolithic integration," IEEE J. Solid-State Circuits, vol. SSC-17, no. 3, pp. 588–591, Jun. 1982.

- [10] V. Brajovic and T. Kanade, "New massively parallel technique for global operations in embedded imagers," in Proc. IEEE Workshop CCDs, Adv. Image Sens., Apr. 1995, pp. 1–6.

- [11] L. Qiang, J. G. Harris, and Z. J. Chen, "A time-to-first spike CMOS image sensor with coarse temporal sampling," Analog Integr. Circuits Signal Process., vol. 47, no. 3, pp. 303–313, Apr. 2006.

- [12] O. Yadid-Pecht and E. R. Fossum, "Image sensor with ultra-high-lineardynamic range utilizing dual output CMOS active pixel sensors," IEEE Trans. Electron Devices—Special Issue on Solid State Image Sensors, vol. 44, no. 10, pp. 1721– 1724, Oct. 1997.

- [13] M. Mase, S. Kawahito, M. Sasaki, Y. Wakamori, and M. Furuta, "A wide dynamic range CMOS image sensor with multiple exposure-time signal outputs and 12-bit column-parallel cyclic A/D converters," IEEE J. Solid- State Circuits, vol. 40, no. 12, pp. 2787–2795, Dec. 2005.

- [14] O. Yadid-Pecht and A. Belenky, "In-pixel autoexposure CMOS APS," IEEE J. Solid-State Circuits, vol. 38, no. 8, pp. 1425–1428, Aug. 2003.

- [15] T. Hamamoto and K. Aizawa, "A computational image sensor with adaptive pixel based integration time," IEEE J. Solid-State Circuits, vol. 36, no. 4, pp. 580–585, Apr. 2001.

- [16] Kulah, H.; Akin, T., "A CMOS current mirroring integration readout structure for infrared focal plane arrays," Solid-State Circuits Conference, 1998. ESSCIRC '98. Proceedings of the 24th European , vol., no., pp.468,471, 22-24 Sept. 1998 doi: 10.1109/ESSCIR.1998.186310

- [17] Kulah, H.; Akin, T., "A Current Mirroring Integration Based Readout Circuitfor High Performance Infrared FPA Applications", IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing,, vol. 50, no.4, pp. 181 - 186, 2003.

- [18] Tepegoz, M.; Akin, T., "A readout circuit for QWIP infrared detector arrays using current mirroring integration," Solid-State Circuits Conference, 2003. ESSCIRC '03. Proceedings of the 29th European , vol., no., pp.133,136, 16-18 Sept. 2003 doi: 10.1109/ESSCIRC.2003.1257090

- [19] Libin Yao, "CMOS readout circuit design for infrared image sensors", CMOS readout circuitry for IR detectors 2009 SPIE