# Simple Technique to Reduce FPN in a linear-logarithm APS

Carlos A. de Moraes Cruz(\*)(\*\*\*), Davies W. de Lima Monteiro(\*\*\*\*), Gilles Sicard(\*\*\*\*) and Alexandre K. P. Souza(\*)

[\*Department of Electronics and Computation, Universidade Federal do Amazonas, Av. Gal. Rodrigo Octávio Jordão Ramos, 3000 - Coroado I 69077-000, Manaus, AM, Brazil. Phone: +55 92 3305 4678. Emails: (agscruz@hotmail.com, alexandre.akps@hotmail.com); \*\*Graduate Program in Electrical Engineering - Federal University of Minas Gerais - Av. Antônio Carlos 6627, 31270-901, Belo Horizonte, MG, Brazil. Email: agscruz@hotmail.com; \*\*\*Department of Electrical Engineering, DEE/PPGEE, Universidade Federal de Minas Gerais, Av. Antonio Carlos, 6627 - Pampulha 31270-010, Belo Horizonte, MG, Brazil. Phone: +55 31 3409-3416. Email: advies@ufmg.br; \*\*\*\*TIMA Laboratory, CNRS, Grenoble INP, UJF, 46, avenue Felix Viallet, 38031 Grenoble, France. Phone: +33 (0)4 76 57 46 42. Email: gilles.sicard@imag.fr]

Abstract— The basic three FET active-pixel-sensor (APS) operating in linear-logarithmic mode yields high-dynamic-range images. However, fabrication non idealities result in fixed-pattern noise (FPN) across the focal-plane array and cannot be reduced by conventional correlated double sampling techniques. Alternative techniques may be used to reduce FPN but they increase the complexity of either the pixel or the external circuitry. In this work a simple technique is proposed to reduce FPN in a modified 3T APS operating in the liner-logarithmic regimen. Simulations show that the proposed technique can reduce the total FPN by more than 80%. The remaining FPN is less than 0.4% of the output signal swing in 120dB.

Keywords-Image Sensor; APS; FPN; Wide Dynamic Range;

#### I. Introduction

Active-Pixel Sensors (APS) are the most ubiquitous choice in CMOS imagers. They operate basically in two modes: linear and logarithmic. The linear mode promotes good sensitivity at low illumination but low dynamic range (DR) towards high illumination. While in the logarithmic mode the APS presents high DR towards high illumination but rather poor sensitivity at low illumination.

To combine good sensitivity to low illumination and high DR towards high illumination, the APS can be operated in the combined linear-logarithmic mode [1]. There are many techniques to achieve high DR that combine linear and logarithmic response [2], but they either increase the pixel complexity or reduce frame rate, by performing multiple-frame captures.

A relevant issue, however, is that when a conventional 3T APS is operated in the logarithmic mode, classical correlated double sampling (CDS) no longer applies, leaving the focal-plane array with a sometimes inordinate amount of Fixed-Pattern Noise (FPN) uncompensated. FPN is caused by pixel-to-pixel output variation under uniform illumination due to component and interconnection mismatches across the array. Column FPN, produced by the column amplifier, is the most recurrent source of FPN in CMOS imagers [7].

Several techniques have been proposed to reduce FPN in the logarithmic mode, as storing the pixel offsets [2], at the cost of added memory and liability to temperature variations; or applying double sampling readout subtraction (DSRS), by producing a voltage or current reference at the sense node of the pixel [3], [4], [5] and [6]; or by multimode readout pixel architectures [7, 8]. Such techniques require more complex pixel circuitry, which therefore reduces its fill factor.

In this work we present extended investigation results of a modified and simple DSRS technique to reduce FPN in the 3T APS operating either in logarithmic or in linear-logarithmic modes [9]. As the proposed technique can be applied directly to the 3T APS, the fill factor can be kept as large as possible.

The proposed technique will be described in section II. Simulations results asserting the solution are shown in section

This work has been supported by the Brazilian agency CAPES, Fundação de Pesquisa do Estado de Minas Gerais - FAPEMIG and Conselho Nacional de Pesquisa - CNPq and has also been realized in the scope of INCT-DISSE.

III. The pixel implantation is discussed in section IV. Finally, conclusions drawn from this work are given in section V.

### II. REDUCING FIXED-PATTERN NOISE

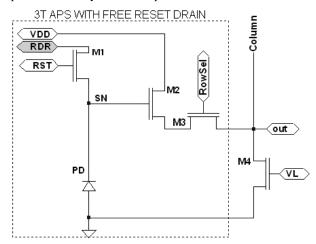

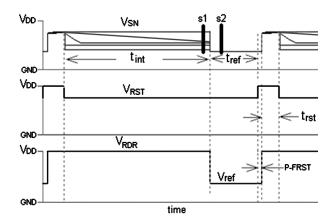

The technique consists in letting the drain of the reset transistor, RDR connection of  $M_1$  in fig. 1, free to be connected at any voltage level and using this particular connection to establish a voltage reference at the sense node for the second output voltage readout during the reference time,  $t_{\rm ref}$  fig. 2. By double sampling the output voltage, the first sample,  $s_1$  in fig. 2, registers the signal and the offset FPN, and the second,  $s_2$  in fig. 2, registers the voltage reference and also great part of the offset FPN. The subtraction of the first sample from the second suppresses the common offset FPN, which is present invariably in both samples.

Figure 1. 3T APS with free reset-transistor drain to apply the voltage reference.

To implement the proposed solution, the set of signal controls shown in fig. 2 can be used to establish the voltage reference. The upper waveform, V<sub>SN</sub>, represents the sensenode signal under five different levels of illumination. When exposed to the three higher levels of illumination V<sub>SN</sub> reaches the logarithmic region in the beginning of integration time, t<sub>int</sub>; and for the other two lower levels, the respective signals remain fairly linear until the end of the integration time. In the same figure, V<sub>RST</sub> represents the reset signal with modulated low level; and V<sub>RDR</sub> represents the signal applied at the drain of M<sub>1</sub> to either bias this transistor, high level, or to produce the voltage reference for the second sampling, low level. P-FRST pseudo-flash reset, meant to reduce image lag [9], and t<sub>rst</sub> stand for the reset time. It is important to notice that the low level of  $V_{RDR}$  must be lower than the lowest possible level of  $V_{SN}$  [9]. The lowest level of V<sub>SN</sub> is reached when the pixel is under the highest illumination condition.

The effectiveness of this technique was evaluated by means of Monte Carlo simulations and the results are shown in the next section.

Figure 2. Double-sampling voltage reference, signal scheme.

# III. SIMULATIONS AND RESULTS

Monte Carlo simulations of the pixel, designed in the AMS CMOS  $0.35\mu m$  technology, was performed to verify the total and reduced FPN across the array, between columns, and along a column where all pixels share the same column amplifier,  $M_4$  fig. 1. The FPN across the array is determined by mismatches of  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$ . The FPN between columns is determined by mismatches of  $M_4$ . And the FPN along a column is determined by mismatches of  $M_1$ ,  $M_2$  and  $M_3$ .

The setup of the signal control in fig. 2 for the linear-logarithmic operation is the following: the  $V_{\rm DD}$  voltage is 3.3V, the reset low level is fixed at 2.5V, and the low level of  $V_{\rm RDR}$  is 1.4V. The illumination level is represented here by photocurrents varying from 1fA to 10uA.

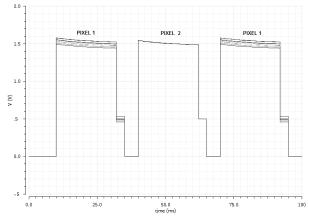

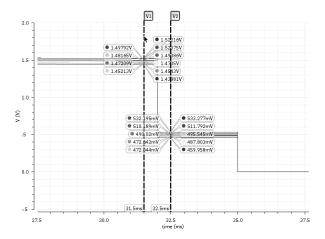

The results presented in this section are the mean and standard deviation of the output of the pixel, before and after FPN correction, of 256 Monte Carlo simulations for each photocurrent. An example of the pixel voltage output in the time for 10 Monte Carlo simulations is given in fig. 3. Each time slot in fig. 3 shows alternately part of the integration and reference times of two different pixels. In the first pixel the mismatches of M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub> and M<sub>4</sub> were applied, while in the second pixel no mismatch was applied. To produce the results for each photocurrent as presented next, the output of pixel 1 was sampled twice, as shown in fig. 4, according to the scheme in fig. 2.

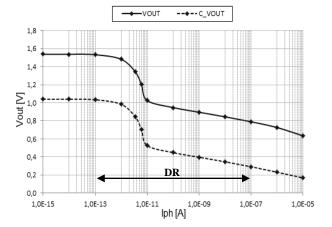

In the dynamic range of 120dB indicated in fig. 5, the output voltage swing after the FPN correction is 743mV that is almost the same before correction, 744mV, as shown in fig. 5. In this graph VOUT and C\_VOUT stand for the output voltage variation for the pixel with illumination before and after FPN correction, respectively.

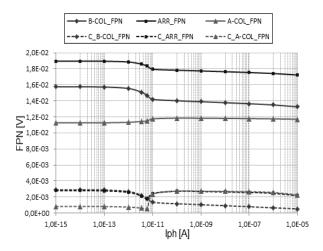

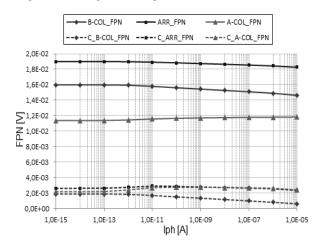

The total and corrected FPN across the array, between columns, and along a column are shown in fig. 6. In this graph ARR\_FPN, B-COL\_FPN and A-COL\_FPN stand for FPN before correction across the array, between columns, and along a column respectively, and C\_ARR\_FPN, C\_B-COL\_FPN and C\_A-COL\_FPN stand for FPN after correction across the array, between columns, and along a column respectively.

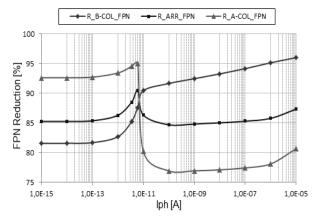

The simulation results have shown a reduction better than 80% of the FPN across the array throughout the complete illumination range, R\_ARR\_FPN in fig. 7. The FPN between columns can be reduced to better than 80% in the low illumination range, and than 90% in the high illumination range, R\_B-COL\_FPN in fig. 7. While the FPN along a

column can be reduced to better than 90% in the low illumination range and than 75% in the high illumination range, R\_A-COL\_FPN in fig. 7.

Figure 3. Ouput for 10 Monte Carlo simulations with Iph of 1pA.

Figure 4. Sampling times.

These results show that, in the linear-logarithmic mode, the maximum FPN across the array in the dynamic range indicated in fig. 5, without correction is about 2.54% of the signal swing in this range. While the maximum FPN across the array with correction is about 0.38% of the signal swing in this range.

This technique can also be applied for the pixel operating in full-logarithmic mode with the reset signal,  $V_{RST}$  in fig. 2, always in  $V_{DD}$ . The  $V_{DD}$  voltage level is still 3.3V, and the low level of  $V_{RDR}$  is shifted to 2.0V. As in the previous case, the illumination level is represented by photocurrents varying from 1fA to 10uA.

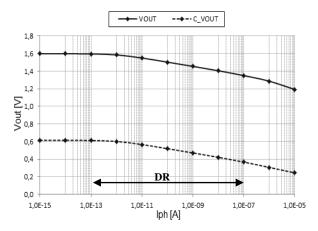

In the dynamic range of 120dB indicated in fig. 8, the output voltage swing after the FPN correction is 246mV that, as in the previous case, is almost the same before correction, 247mV, as shown in fig. 8. In this graph VOUT and C\_VOUT stand for the output voltage variation for the pixel with illumination before and after FPN correction, respectively.

Comparing with the results of the linear-logarithmic mode, presented above, fig. 5, the full-logarithmic mode has reduced sensitivity especially in the low illumination region. The signal swing in linear-logarithmic mode is three times higher than

that in full-logarithmic mode either with or without FPN correction.

Figure 5. Linear-logarithmic output before and after FPN correction.

Figure 6. Total and corrected in linear-logarithmic mode.

Figure 7. Percentage of FPN reduction in linear-logarithmic mode.

The total and corrected FPN across the array, between columns, and along a column are shown in fig. 9. In this graph ARR\_FPN, B-COL\_FPN and A-COL\_FPN stand for FPN before correction across the array, between columns, and along a column respectively, and C\_ARR\_FPN, C\_B-COL\_FPN and

C\_A-COL\_FPN stand for FPN after correction across the array, between columns, and along a column respectively.

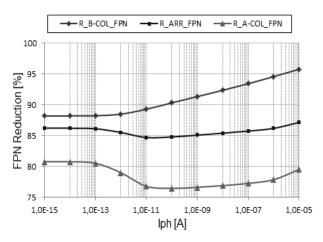

The simulation results have shown a reduction better than 80% of the FPN across the array throughout the complete illumination range, R\_ARR\_FPN in fig. 10. The FPN between columns can be reduced to better than 85% in the complete illumination range, R\_B-COL\_FPN in fig. 10. While the FPN along a column can be reduced to better than 75% in the complete illumination range, R\_A-COL\_FPN in fig. 10.

These results show that, in the full-logarithmic mode, the maximum FPN across the array in the dynamic range indicated in fig. 8, without correction is about 7.70% of the signal swing in this range. While the maximum FPN across the array with correction is about 1.17% of the signal swing in this range.

These results show a true improvement in FPN reduction for active pixel sensors working in full-logarithmic mode when compared with some previous results in the literature. The solution in [4], using a 5T NMOS pixel in a CMOS 0.5µm technology, has a signal swing of 300mV in 120dB, and achieves a remaining FPN of 2.5% of the signal swing in this range. The solution in [5], using a 4T PMOS pixel in the same CMOS 0.35µm technology, has a signal swing of 231mV in 120dB, and achieves a remaining FPN of 2.9% of the signal swing in this range. The solution in [6], using a 5T PMOS pixel in the same CMOS 0.35 µm technology, has a signal swing of 705mV in 120dB, and achieves a remaining FPN of 2.1% the signal swing in this range. Whereas the results obtained with our pixel operating in the linear-logarithmic regimen are much better, with a signal swing of 743mV in 120dB, and a remaining FPN of 0.38% of the signal swing in

# IV. PIXEL IMPLEMENTATION

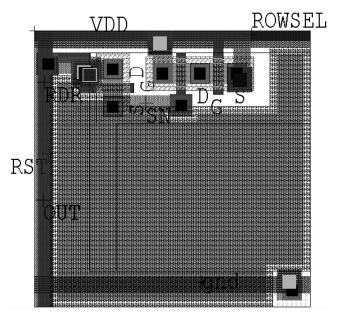

The great advantage of the proposed technique in relation to the previous solution is the use of only three FETs in the APS, exactly as in the basic 3T APS. However, the proposed pixel uses an additional line connection for the drain of the reset transistor, RDR in fig. 1. Due to this additional connection the fill factor of the proposed pixel may be slightly reduced compared to that of the basic 3T APS.

The proposed 3T APS, the schematic diagram of which is shown in fig. 1, has been designed in the AMS standard 4-metal 2-poly CMOS  $0.35\mu m$  technology. The layout of pixel shown in fig. 11 has the following characteristics: pixel size  $10\mu m \times 10\mu m$  and fill factor of 56%.

## V. CONCLUSIONS

The proposed technique provides a simple way to reduce FPN in the linear-logarithmic APS. This is achieved with a minor modification to the conventional 3T pixel design and control-signal scheme, and has been evaluated by Monte Carlo simulations. The technique is also effective to reduce FPN in the full-logarithmic APS. The pixel complexity and size is kept low, and its fill factor can be as high as that of the basic 3T APS, though it suffers a slight reduction due to the additional connection line for RDR. This solution, based on simple modification revisiting an established pixel topology, leads to improved CMOS image sensor at no additional fabrication cost.

Figure 8. Full-logarithmic output before and after FPN correction .

Figure 9. Total and corrected FPN in full-logarithmic mode.

Figure 10. Percentage of FPN reduction in full-logarithmic mode.

Figure 11. Layout of a 10μm x 10μm pixel with a fill factor of 56%.

#### REFERENCES

- M. Wäny, "Photodetector and method for detecting radiation," U.S. Patent 6 815 685 B2, November 9th, 2004. Provisional application No. 10/148 683, filed on December 21st, 2000.

- [2] A. El Gamal, "High dynamic range image sensors," In Tutorial at International Solid-State Circuits Conference, Feb. 2002.

- [3] M. Loose, K. Meier, and J. Schemmel, "A self-calibrating single-chip CMOS camera with logarithmic response", IEEE Journal of Solid-state circuits, vol.36, n° 4, April 2001.

- [4] S. Kavadias, B. Dierickx, D. Scheffer, A. Alaerts, D. Uwaerts, J. Bogaerts, "A Logarithmic Response CMOS Image Sensor with On-Chip Calibration," IEEE Journal of Solid-State Circuits, vol. 35, pp. 1146-1152, August 2000.

- [5] E. Labonne, G. Sicard, M. Renaudin, "An on-pixel reduction method for a high dynamic range CMOS imager", IEEE European Solid State Circuits Conference ESSCIRC, Munich, Germany, September 2007.

- [6] H. Amhaz and G. Sicard, "A high output voltage swing logarithmic image sensor designed with on chip FPN reduction," Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), pp. 1-4, July 2010.

- [7] M. Tabet, "Double Sampling Techniques for CMOS Image Sensors," Doctoral Thesis, UMI Order No. AAT NQ77247, University Waterloo, 2002

- [8] N. Akahane, R. Ryuzaki, S. Adachi, K. Mizobuchi and S. Sugawa, "A 200dB Dynamic Range Iris-less CMOS Image Sensor with Lateral Overflow Integration Capacitor using Hybrid Voltage and Current Readout Operation," IEEE International Solid-State Circuits Conference, Digest of Technical Papers, pp. 1161-1170, February 2006.

- [9] C.A. de Moraes Cruz, D.W. de Lima Monteiro and I.L. Marinho, "Extended use of Pseudo-Flash Reset Technique for an Active Pixel with Logarithmic Compressed Response," In Proceedings of 25th Symposium on Integrated Circuit and System Design, SBCCI, Brasilia-BR, Aug.-Sep. 2012.