## A 1.2MP 1/3" Global Shutter CMOS Image Sensor with Pixel-Wise Automatic Gain Selection

Johannes Solhusvik<sup>1</sup>, Sergey Velichko<sup>2</sup>, Trygve Willassen<sup>1</sup>, Sohrab Yaghmai<sup>1</sup>, Jenny Olsson<sup>1</sup>, Anders Rosnes<sup>1</sup>, Tore Martinussen<sup>1</sup>, Per Olaf Pahr<sup>1</sup>, Siri Eikedal<sup>1</sup>, Steve Shaw<sup>3</sup>, Ranjit Bhamra<sup>3</sup>, Dan Pates<sup>2</sup>, Scott Smith<sup>2</sup>, Lingtao Jiang<sup>2</sup>, David Wing<sup>2</sup>, Jenny Bai<sup>2</sup>, Satyadev Nagaraja<sup>2</sup>, Ajaya Chilumula<sup>2</sup>

<sup>1</sup>Aptina Norway AS, Oslo, Norway,

<sup>2</sup>Aptina, LLC, San Jose, CA, USA,

<sup>3</sup>Aptina (UK) Limited, Bracknell, UK

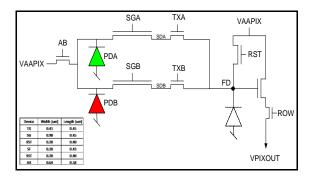

A 1280x960 45fps CMOS image sensor with global shutter is presented. Main novelties are (i) 3.75  $\mu m$  pixel pitch which is smallest GS pixel pitch published to date in CMOS, and (ii) per-pixel automatic gain selection (AGS) which improves intra-scene dynamic range. The pixel circuit is illustrated in fig.1. A vertical two-way shared architecture yields four transistors per pixel (4T) compared to 6T in a non-shared configuration. Each pixel has a storage gate transistor (SGA or SGB) which controls charge transfer from photodiode (PDA or PDB) to the storage diode (SDA or SDB).

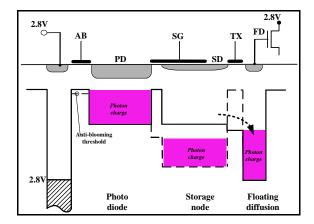

The storage gate (SG) and its accompanying storage diode (SD) act as a photon-charge storage node as illustrated in the pixel cross section in fig.2. Since the storage node is electrically isolated from the floating diffusion (FD) correlated double-sampling (CDS) readout is supported. Each pixel row-pair has an extra reset transistor (labeled AB) which can be turned ON to drain charge from the photodiode (PD) to 2.8V power supply. This can occur simultaneously to, and without impacting, the CDS readout process. Thus, a new image capture can commence whilst reading out the previous frame. Note that since AB is globally controlled it too can be shared between two rows to save area. During photon integration the voltage on AB gate is kept slightly positive to act as an anti-blooming drain.

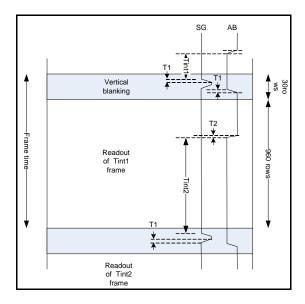

A high-level timing diagram for global shutter capture operation is illustrated in fig.3. The vertical axis represents time and starts with 30 row-times of vertical blanking (VB). Inside this VB phase SG is pulsed to transfer the captured image from PD to SD. Reference pixels for offset calibration are read out during VB. Thereafter, frame readout can commence, i.e. CDS readout of all rows sequentially until the end of the array. During frame readout a new picture can be captured by turning OFF the AB gates which initiates PD photon integration. At the end of integration (and frame readout) SG is pulsed again to freeze and store the captured frame, and the readout process can re-commence.

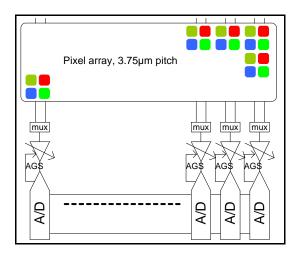

Fig.4 illustrates the analog readout architecture. Column-parallel and top-bottom readout was selected to minimize power and read-noise. Note that the top section of the readout block (above the array) is omitted in fig.4 for simplicity. Every column-pair has a 2:1 multiplexer (MUX), a 1x, 2x, 4x, 8x configurable gain amplifier, and a 12-bit successive approximation (SA) ADC running at up to 750kpix/sec. The

CDS and A/D conversion process for one row takes approximately  $5.5 \mu s$ .

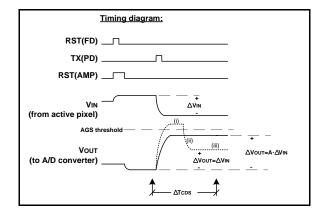

The CDS readout includes automatic gain selection (AGS) which is used to suppress noise contribution from the ADC when sensor operates in unity gain mode. AGS operates on a per-pixel basis and involves three phases as illustrated in fig.5: (i) compare pixel output against threshold, (ii) adjust gain accordingly, (iii) allow amplifier output to settle and then start A/D operation. The pixel signal level is measured after CDS and compared against a fixed voltage threshold approximately equal to Vref/G<sub>HI</sub>. The comparator (re-used from ADC) output signal is routed to the differential column amplifier to select which gain to use, i.e. either  $G_{HI}$  (8x, 4x or 2x) or  $G_{LO}$  (1x). This gain select bit is also used in the digital signal processing path to linearize the pixel output value. To avoid non-linearity issues, the G<sub>HI</sub>/G<sub>LO</sub> gain ratio value must be precisely measured. This is done during vertical blanking time using dedicated reference pixels read out with high and low gain. It is worth noting that area and power penalty for AGS is kept small thanks to re-using the comparator belonging to the ADC.

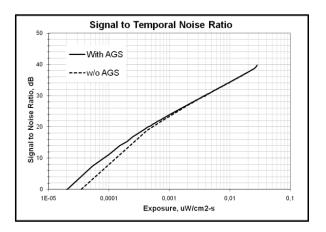

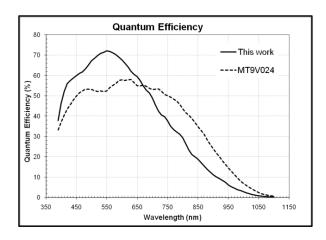

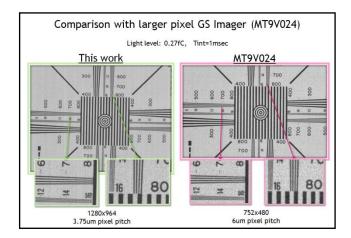

The imager was fabricated in a 2.8V 130nm CMOS 2LP4LM process. Initial results on monochrome pixels without any process tuning or design optimization are provided in below plots and tables. A comparison is made with a 6μm GS product (Aptina's MT9V024). Overall conclusion is that light sensitivity and noise level is excellent and outperforms the 6μm imager, virtually no lag is observed, and the AGS function performs as predicted.

Shutter efficiency on initial silicon is measured to 310:1. In comparison, minimum acceptable shutter efficiency in interline CCDs is in the order of 1000:1 or better. Our goal is to reach this value after process tuning and optimization of optical stack and readout timing.

## REFERENCES

[1] S. Lauxtermann, A. Lee, J. Stevens, and A. Joshi, "Comparison of global shutter pixels for CMOS image sensors," in *Proc. Int. Image Sensor Workshop*, Jun. 2007, pp. 82–85.

[2] N. Bock, A. Krymski, A. Sarwari, M. Sutanu, N. Tu, K. Hunt, M. Cleary, N. Khaliullin, and M. Brading, "A wide-VGA CMOS image sensor with global shutter and extended dynamic range," in *Proc. IEEE Workshop CCDs Adv. Image Sensors*, Jun. 2005, pp. 222–225.

[3] K. Yasutomi, S. Itoh, and S. Kawahito, "A Two-Stage Charge Transfer Active Pixel CMOS Image Sensor With Low-Noise Global Shuttering and a Dual-Shuttering Mode," in *IEEE Trans on Electron Devices, Vol. 58, No. 3, March 2011*.

[4] N. Teranishi, A. Kohno, Y. Ishihara, and K. Arai, "No image lag photodiode structure in the interline CCD image sensor," in *IEDM Tech. Dig.*, Dec. 1982, pp. 324–327.

Fig.1

Fig.2

Fig.3

Fig.4

Fig. 5

Fig. 6

Fig.7

Fig.8

| Parameter                    | Symbol     | Units       | MT9V024    | This work  |

|------------------------------|------------|-------------|------------|------------|

| Readout noise                | st         | е           | 21.9       | 2.4        |

| Photoresponse non-uniformity | PRNU       | %           | 0.76       | 0.86       |

| Row/Column FPN at 50% signa  | Row/CoIFPN | %           | 0.09, 0.19 | 0.10, 0.22 |

| Dark signal non-uniformity   | DSNU       | %           | 0.48       | 0.18       |

| Non-linearity                |            | %           | +3/-3      | +1/-1.5    |

| Total SNR at 50% signal      | SNR        | dB          | 38.0       | 33.5       |

| Dynamic Range                | DynR       | dB          | 58.1       | 69.0       |

| Responsivity                 | R          | Ke/µW/cm2*s | 551        | 289        |

| Linear Full-well Capacity    |            | Ke          | 17.5       | 7.5        |

| Discharging Lag @ 40%        | DL40%      | %           | <0.5       | 0.01       |

| Charging Lag @ 40%           | CL40%      | %           | <0.5       | 0.05       |

| Max Quantum Efficiency       | QEmax      | %           | 55.3       | 73.6       |

| MTF at 80 cys/mm             | MTF80c/mm  |             | 0.35       | 0.58       |

| Global Shutter Efficiency    | GSE        | %           | 1000:1     | 310:1      |

Table 1