## Process Integration aspects of back illuminated CMOS Imagers using Smart Stacking TM technology with best in class direct bonding

Ruth Shima Edelstein<sup>1</sup>, Omer Katz<sup>1</sup>, Becky Lavi<sup>1</sup>, Ishai Aberman<sup>1</sup>, Sagee Rosenthal<sup>1</sup>, Michal Shadmi<sup>1</sup>, Shay Arad<sup>1</sup>, Nili Golan<sup>1</sup>, Michal Shach Caplan<sup>1</sup>, and Morad Massalha<sup>1</sup>.

Chrystelle Lagahe-Blanchard<sup>2</sup>, Laurent Marinier<sup>2</sup>, Richard Fontanière<sup>2</sup>, Arnaud Castex<sup>2</sup>, Marcel Broekaart<sup>2</sup>, Muriel Martinez<sup>2</sup>, Nathalie Milhet<sup>2</sup>, Arnaud Rigny<sup>2</sup>, Christine Pelissier<sup>2</sup>

- (1) TowerJazz, Ramat Gavriel Industrial Area, P.O. Box 619, Migdal Haemek, Israel 23105, Tel: +972-4-650-6611, Fax: 972-4-6547788, E-mail: <a href="mailto:ruthsh@towersemi.com">ruthsh@towersemi.com</a>

- (2) SOITEC, Parc technologique des Fontaines, Bernin 38926 Crolles Cedex, France Tel: +33 (0)4 76 92 96 31, Fax: +33 (0)4 76 92 94 31, Email: chrystelle.lagahe@soitec.fr

Over recent years, the concept of backside illuminated (BSI) sensors has become one of the leading solutions to optical challenges such as improved quantum efficiency, and angular dependence. It has been shown advantageous for small pixels [1-6] with limited number of transistors, but is becoming appealing also for high end sensors which require more transistors, fast routing, and large chief ray angles. A 5.4um pixel for cinematography/DSLR with state of the art performance has been fully integrated (0.18 technology) using SOI wafers and Smart Stacking technology to form a BSI sensor.

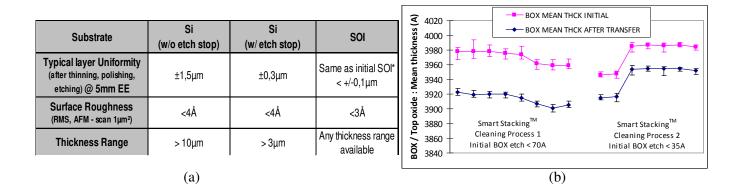

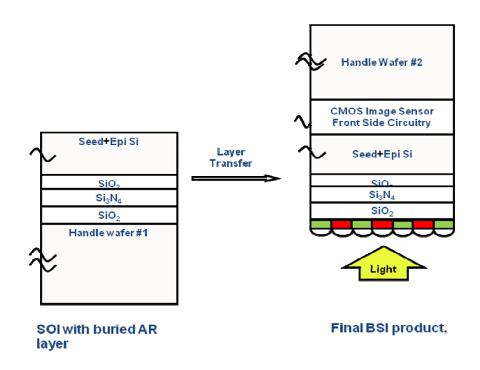

The choice of SOI substrates over bulk material is strongly driven by integration considerations. The buried oxide of the SOI acts as a built-in etch stop [1-4] as well as protection to the active Si layer during the thinning process, making the process less complex and more robust due to highly uniform thinning (fig 1). In addition, the buried layer can be tailored to have anti reflective (AR) properties for various applications (fig 2). In contrast to AR layers which are formed ex situ over back thinned bulk material, wherein the inherent across wafer thickness variation and Si roughness are relatively large, this method uniquely enables very high control over thickness uniformity, and minimizes post processing steps.

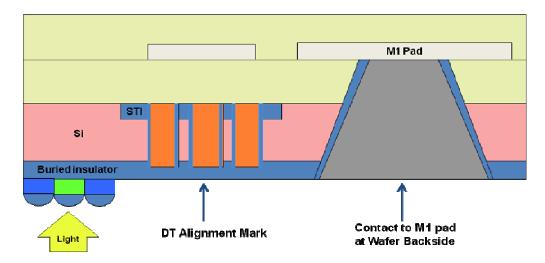

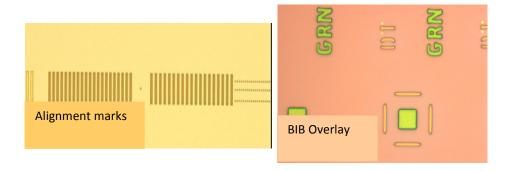

Another significant novel component of our integration is the ability to perform backside alignment of a color filter array, and contacts to pads with lithography tools which are commonly used for front side processing. This achievement is obtained by the formation of deep trenches at the initial steps of processing which land on the buried insulator (fig 3) and are visible from wafer backside (fig 4). These trenches can be customized to the desired Si thickness and therefore a variety of applications. The processed SOI wafer, with CMOS sensor circuitry is then bonded and thinned by the Smart Stacking<sup>TM</sup> technology enabling the transfer of the processed layer onto a handle silicon wafer [7,8].

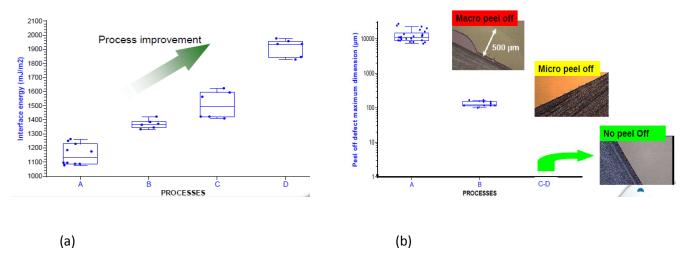

Direct bonding of two wafers requires stringent control of surface properties: micro-roughness, flatness, contamination and surface chemistry in order to achieve high quality bonding in terms of defectiveness, edge exclusion, strength and reliability. Figure 5 compares bonded structures resulting from non optimized and optimized process integration, including adaptation and tuning of alignment marks design (which impose large topography) and fabrication, surface planarization and pre-bonding surface preparation. A defect free bonding interface is achieved with a regular <1.5mm peripheral non bonded width [9,10]. To address thermal budget constraints (i.e.<400°C), specific pre-bonding surface conditioning (CMP, plasma activation,..), and post-bonding thermal treatment were developed to control and increase the bonding strengths. High bonding energies compatible with subsequent processes (thinning, etching, metal deposition, dicing...) were achieved (fig 6), as well as minimized stress. Reducing process-induced distortion is key to avoid impairing devices performance, yield and reliability.

To conclude, we successfully produced a back thinned cinematography/DSLR CMOS image sensor, overcoming integration challenges related to backside processing such as incorporation of a buried AR layer, and backside alignment, by use of SOI substrates and Smart Stacking<sup>TM</sup> technology with best in class direct bonding.

Fig 1: a) Silicon thickness and uniformity performance after layer transfer, depending on initial substrate choice; b) BOX thickness and uniformity after layer transfer based on circuits built on SOI substrates.

Fig 2: Using SOI wafers with buried AR layer to form a BSI sensor.

Fig 3: Schematic of integration showing deep trench alignment marks reaching wafer backside.

Fig 4: Alignment marks and overlay measurement structures visible at wafer backside by optical microscope.

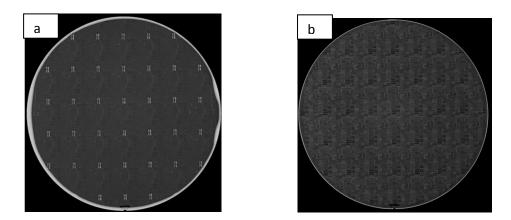

Fig 5: a) Non optimized alignment marks design and planarization process, leading to residual local bonding defects on alignment marks and irregular peripheral non bonded width; b) Optimized process integration.

Fig 6: Best in class direct bonding: a) Various bonding processes and associated interface energies; b) Transferred layer edge quality versus bonding processes [9].

## References:

- 1. Jens Prima et al;" Improved colour separation for a backside illuminated image sensor with 1.4 μm pixel pitch", IISW 2009

- 2. *Y.Kohyama et al*; "A 1.4 μm Pixel Backside Illuminated CMOS Image Sensor with 300 mm Wafer Based on 65 nm Logic Technology"; IISW 2009

- 3. Hayato Wakabayashi et al, A ½.3 inch 10,3 Mpixel 50frames/s Back-Illuminated CMOS Image Sensor ISSCC 2010,p 410.

- 4. *Tom Joy et al*; "Development of a Production-Ready, Back illuminated CMOS Image sensor with Small Pixels, IEDM 2007, Washington DC).

- 5. S.G. Wuu et al; "A Manufacturable Back-Side Illumination Technology using Bulk-Si Substrate for Advanced CMOS Image Sensor", IISW 2009.

- 6. H. Rhodes et al: "The Mass Production of BSI CMOS Image Sensors", IISW 2009.

- 7. Soitec website: www.soitec.com

- 8. *C. Lagahe et al*, "Wafer stacking: key technology for 3D integration", IEEE International SOI conference, San Francisco, October 2009.

- 9. A. Castex et al, "Low Temperature Direct Wafer Bonding Process for Back Side Illumination Image Sensors and 3D Stacking", IEEE conference Low Temperature Bonding for 3D Integration, Tokyo, January 2010.

- 10. A. Castex et al, "Edge Bonding Void Free Low Temperature Oxide-Oxide Direct Bonding Process", ECS Spring Conference, Montreal, May 2011.