# Fully depleted, BSI CCDs on high-resistivity silicon

# 2009 IISW Symposium on Back Illumination of Solid-State Image Sensors

June 25th, 2009

Steve Holland

Lawrence Berkeley National Laboratory

UNIVERSITY OF CALIFORNIA OBSERVATORIES / LICK OBSERVATORY

#### **Introduction to Lawrence Berkeley National Laboratory**

LBNL is one of the U.S. Department of Energy's national laboratories, and is managed for the DOE by the University of California

The Laboratory conducts unclassified research and has an annual budget of approximately \$600 million U.S. dollars

Founded in 1931 by Ernest Lawrence, the Laboratory employs ~ 4000 scientists, engineers, and support staff

The CCD development work is done under the auspices of the Physics Division with major support from the Engineering Division

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

## Impact of fully depleted, back-illuminated CCDs on astronomy and astrophysics

• Many major camera upgrades at ground-based telescopes are using or are planning to use fully depleted, back-illuminated CCDs:

- —Subaru Super and HyperSuprime Cameras

- 10, 2048 x 4096 (15 μm pixel), 200 μm thick, fully depleted p-channel CCDs in operation since August 2008 (Super Suprime-Cam)

- —<u>http://www.naoj.org/Pressrelease/index\_2008.html#081120</u>

- HyperSuprime-Cam will require ~ 200 CCDs

- Fabricated by Hamamatsu Corporation

### **Commercial development of FD CCDs**

2k x 4k CCDs fabricated at Hamamatsu Corporation for the Subaru Telescope

http://www.naoj.org/Pressrelease/index\_2008.html#081120

# Impact of fully depleted, back-illuminated CCDs on astronomy and astrophysics

#### —Pan-Starrs (University of Hawaii)

- 1.4 Gpixel camera, 1 installed August 2007 with 3 more proposed

- MIT Lincoln Laboratory orthogonal transfer, 75  $\mu m$  thick fully depleted n-channel CCDs fabricated on  $\sim$  5 k $\Omega$ -cm, p-type silicon

- 60,  $\sim$  5k x 5k (10 µm pixel) CCDs per camera

- http://pan-starrs.ifa.hawaii.edu/public/

- Similar project: WIYN Observatory One-degree imager

# Impact of fully depleted, back-illuminated CCDs on astronomy and astrophysics

### —Pan-Starrs (University of Hawaii) cont'

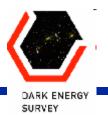

Images from Pan-Starrs 1 Camera

Early 2008 commissioning

## Impact of fully depleted, back-illuminated CCDs on astronomy and astrophysics (cont')

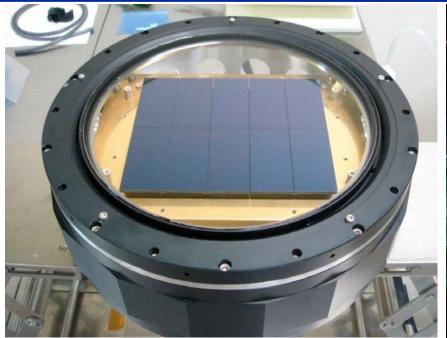

#### —Dark Energy Survey camera

- 62, 2048 x 4096 (15 μm pixel), 250 μm thick, fully depleted p-channel CCDs (~ 0.5 Gigapixel camera)

- Fabrication at DALSA/Lawrence Berkeley National Laboratory, packaging and testing at Fermi National Accelerator Laboratory

- http://www.darkenergysurvey.org/

#### —Large Synoptic Survey Telescope (LSST)

- ~ 200, 4k x 4k (10 μm pixel), 100 μm thick, fully depleted CCDs required (~ 3.2 Gigapixel camera)

- <a href="http://www.lsst.org/lsst/science/concept\_camera">http://www.lsst.org/lsst/science/concept\_camera</a>

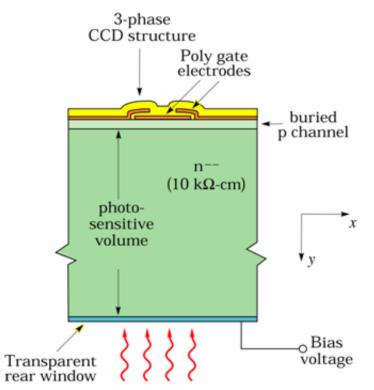

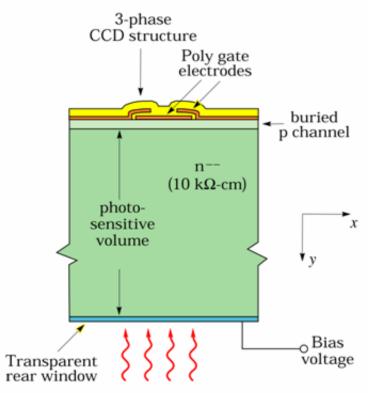

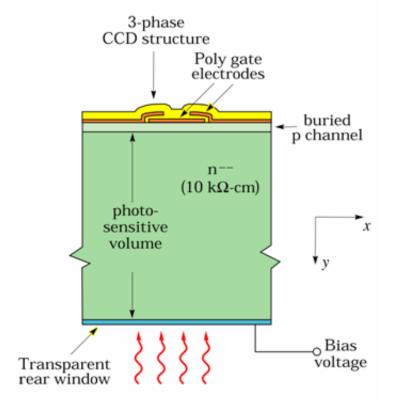

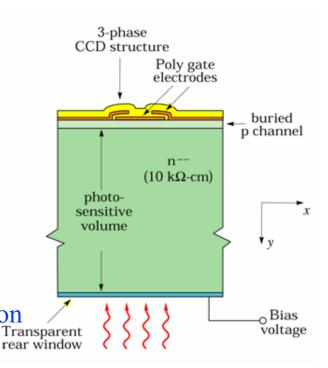

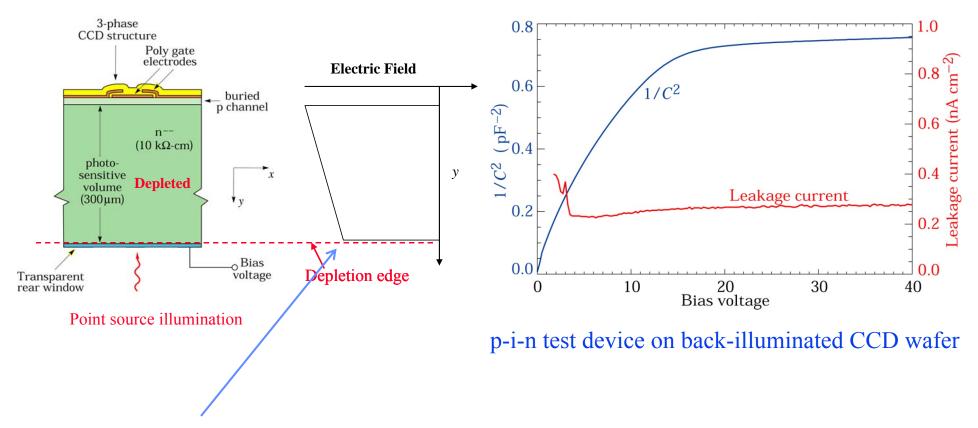

- 1) Concept: Fabricate a conventional CCD on a thick, high-resistivity silicon substrate 200-250 μm typical, 675 μm in special cases

- Use a substrate bias voltage to fully deplete the substrate of mobile charge carriers

Merging of p-i-n and CCD technology

High-ρ Si allows for low depletion voltages

- 3) The thickness results in high near-infrared quantum efficiency and greatly reduced fringing

- 4) The fully depleted operation results in the ability to control the spatial resolution via the thickness and the substrate bias voltage

- 1) Concept: Fabricate a conventional CCD on a thick, high-resistivity silicon substrate 200-250 μm typical, 675 μm in special cases

- 2) Use a substrate bias voltage to fully deplete the substrate of mobile charge carriers

Merging of p-i-n and CCD technology

High-ρ Si allows for low depletion voltages

- 3) The thickness results in high near-infrared quantum efficiency and greatly reduced fringing

- 4) The fully depleted operation results in the ability to control the spatial resolution via the thickness and the substrate bias voltage

10 kΩ-cm corresponds to a doping level of  $\sim 4 \times 10^{11}$  cm<sup>-3</sup>, or about 1 part in  $10^{11}$

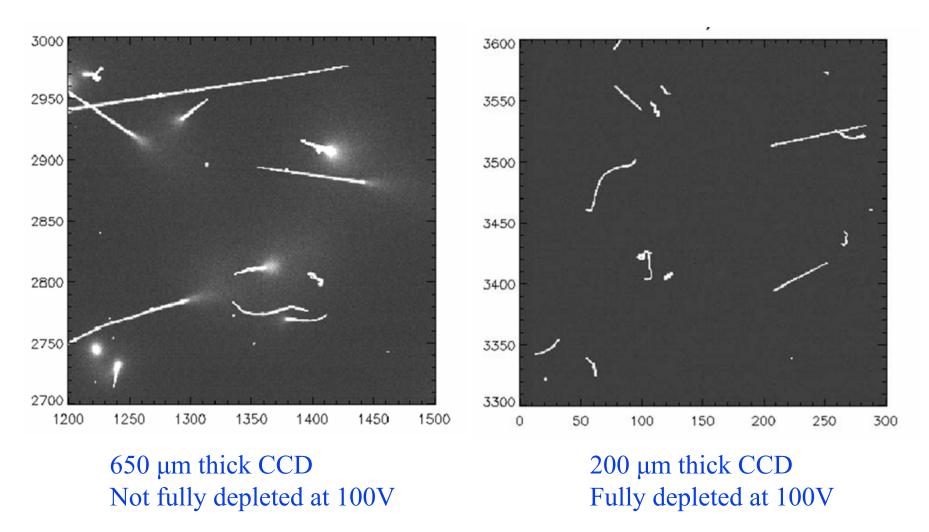

Drawbacks of thick, fully depleted CCDs:

- 1) Charged particles leave ionizing tracks

Cosmic rays, Compton electrons

More pixels affected than in a thin CCD

- 2) Imaging with long wavelength light could result in degraded spatial resolution when fast optics are used

- 3) Surface "pinning" methods to reduce surface dark current are not straightforward to implement when large substrate bias voltages are used

- 4) Susceptible to backside defects, especially for overdepleted operation

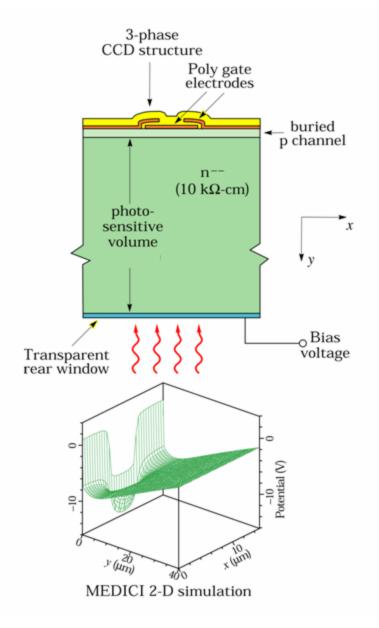

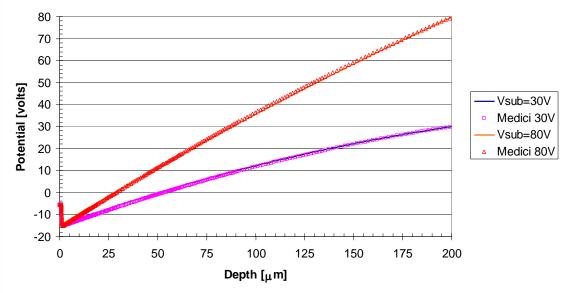

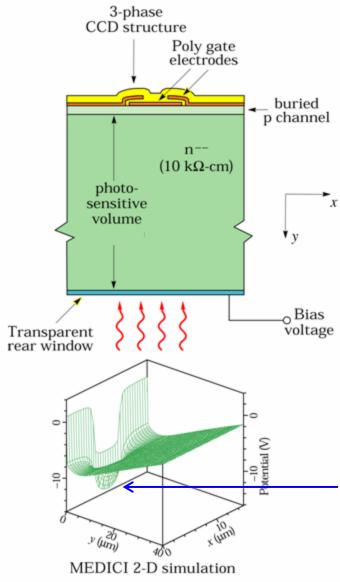

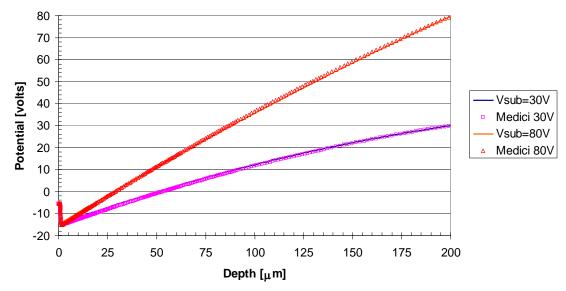

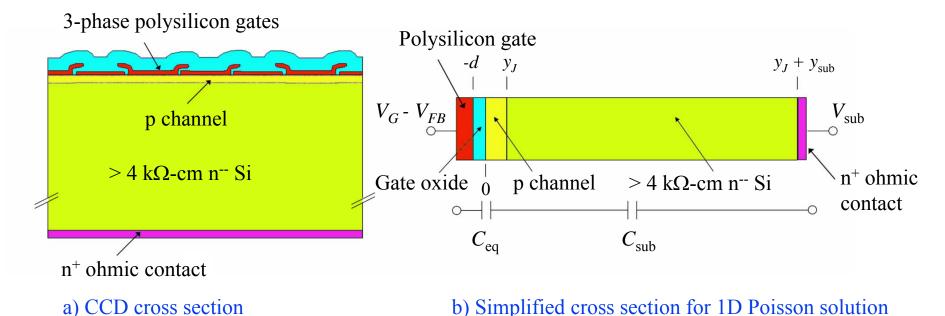

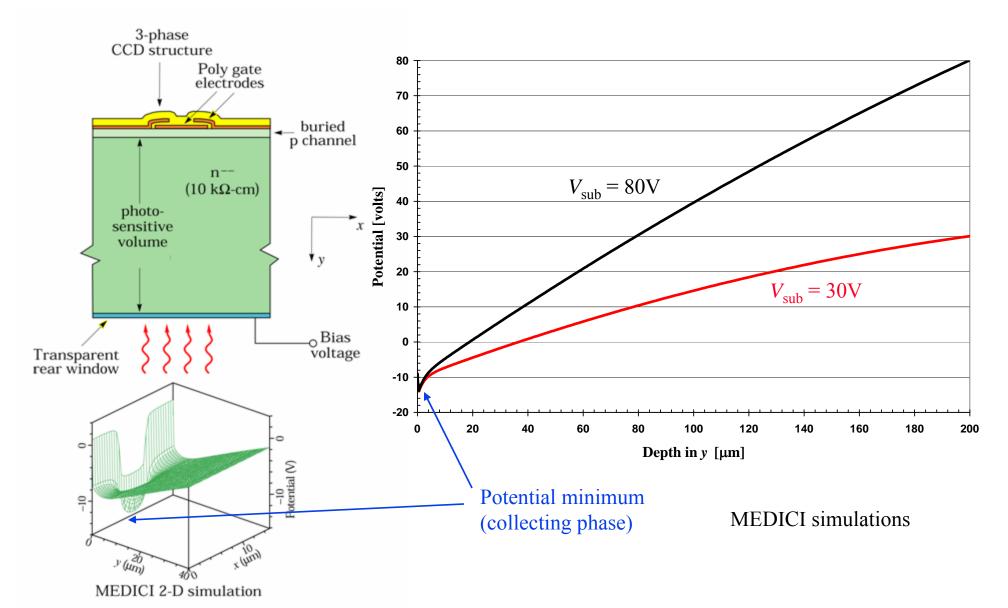

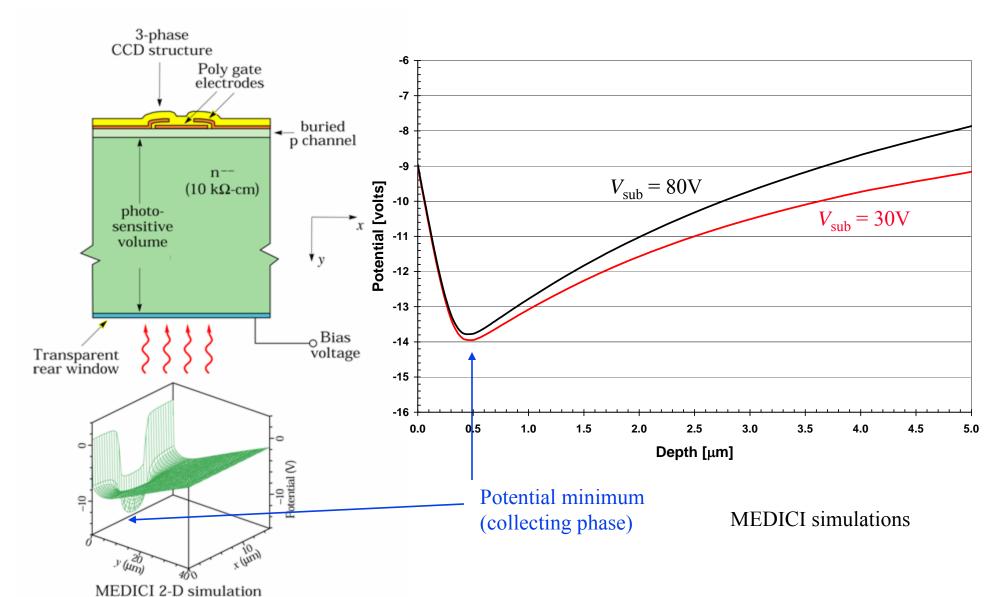

Potential versus depth along center of pixel 1-D potential calculations and Medici simulation

The fully depleted operation produces a drift field throughout the detector substrate

Potential versus depth along center of pixel 1-D potential calculations and Medici simulation

The fully depleted operation produces a drift field throughout the detector substrate

The value of the CCD potential minimum, where holes are collected, is not a strong function of the substrate bias voltage, and as a result operation over a wide range of substrate bias voltages is possible

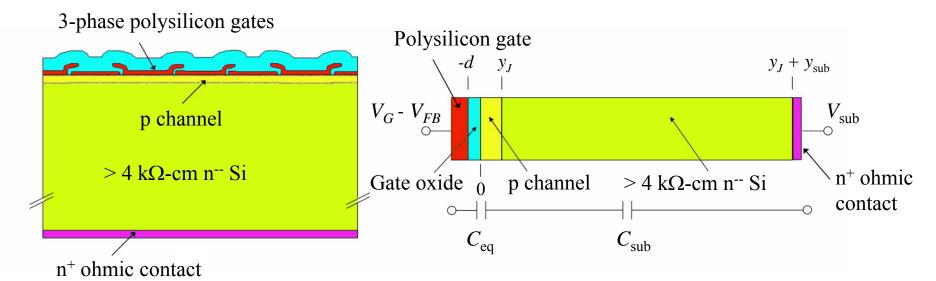

a) CCD cross section

b) Simplified cross section for 1D Poisson solution

Solution to 1-D Poisson equation (depletion approximation, IEEE Trans. Elec. Dev., **50**, 225, 2003):

$$V(y_{J}) = V_{J} \approx V_{G} - V_{FB} - \frac{qN_{A}}{2\varepsilon_{Si}} y_{J}^{2} (1 + \frac{2\varepsilon_{Si}d}{\varepsilon_{SiO_{2}}y_{J}}) \text{ independent of } V_{SUB}$$

$$Valid \text{ for } N_{D,sub} << N_{A} \text{ and } y_{SUB} >> y_{J} + (\frac{\varepsilon_{Si}}{\varepsilon_{SiO_{2}}})d$$

Substrate doping

$$Channel \text{ doping}$$

$$Capacitor \text{ voltage divider}$$

#### **CCD** development at LBNL

- The CCDs developed at LBNL for astronomy and astrophysics are operated at cryogenic temperatures for ultra-low dark current (-100 -140°C typical), and are read out slowly for low noise (50–100 kpixels/sec typical)

- The CCD developed at LBNL is a p-channel CCD

- —Information is carried by holes, not electrons

- —The choice of p-channel CCDs was due to our p-i-n diode experience with n-type, high-resistivity silicon substrates

- Easier to achieve low dark current when compared to p-type silicon

- —An unexpected bonus of the choice of p-channel is enhanced resistance to the effects of space protons in p-channel CCDs

- Charge transfer efficiency degradation much less in p-channel

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- The 200-250 µm thickness gives good near-infrared response

- Fringing due to multiply reflected light is reduced

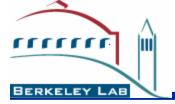

- The blue response is enhanced with a thin, backside n<sup>+</sup> layer

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

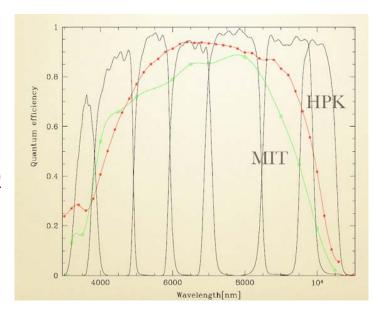

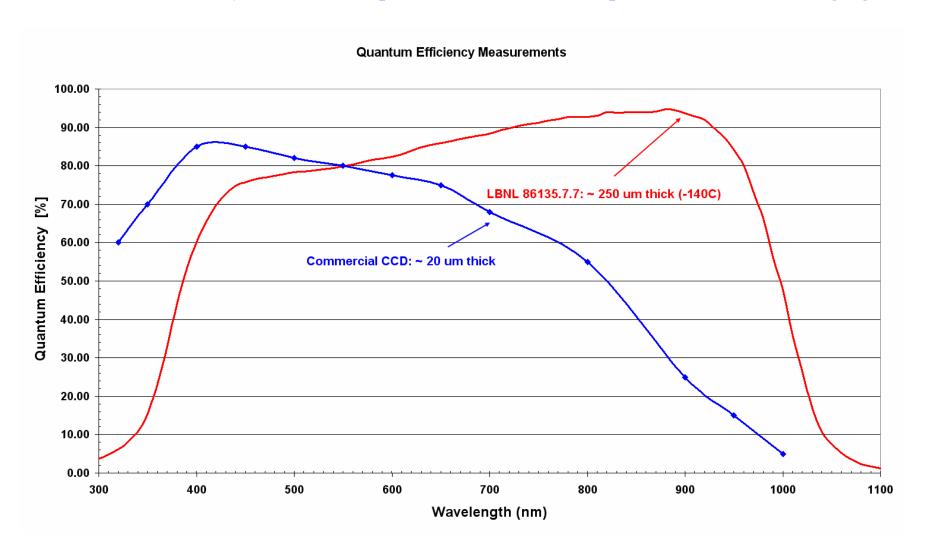

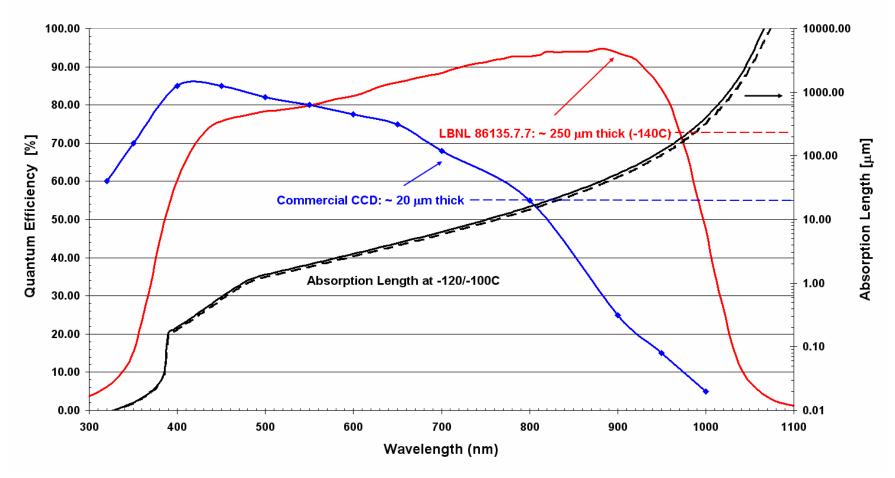

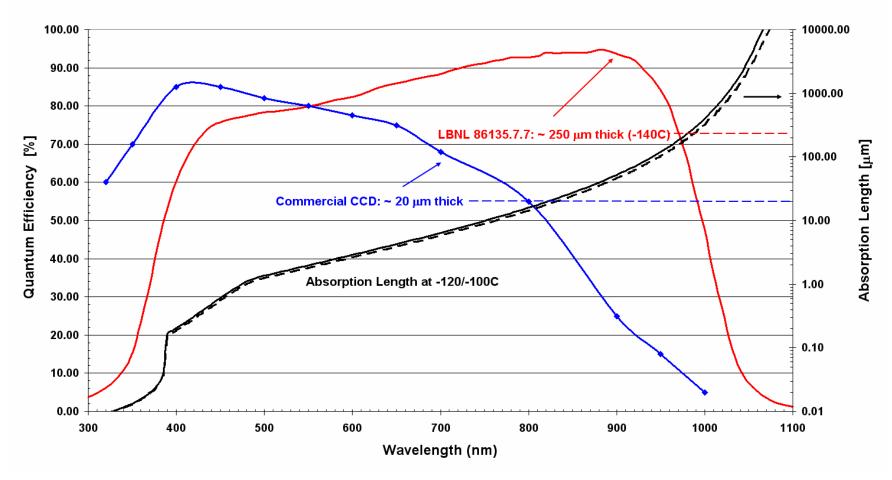

#### **Quantum efficiency**

A key advantage of thick CCDs ( $\sim$ 200–300 µm thick) compared to thinned scientific devices ( $\sim$ 10–20 µm thick) is improved near infrared response and reduced fringing

#### **Quantum efficiency**

A key advantage of thick CCDs ( $\sim$ 200–300 µm thick) compared to thinned scientific devices ( $\sim$ 10–20 µm thick) is improved near infrared response and reduced fringing

#### **Quantum Efficiency Measurements**

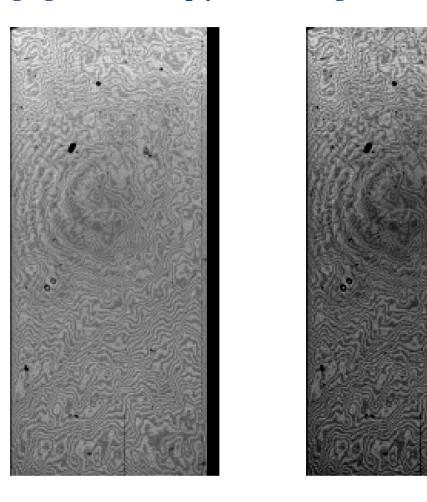

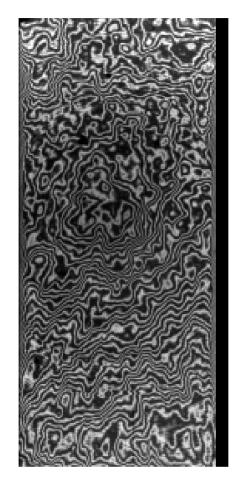

#### Fringing due to multiply-reflected light (uniform illumination, 10–20 µm thick CCD)

$\lambda = 800 \text{ nm}$  900 nm 1  $\mu$ m Measurements courtesy of R. Stover, M. Wei of Lick Observatory

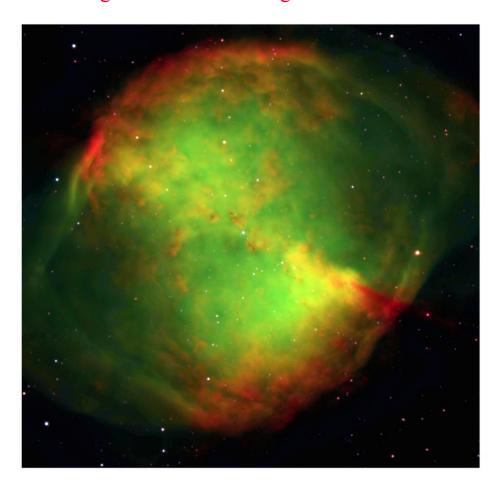

#### Near IR vs Visible image (Dumbbell nebula)

ESO image at visible wavelengths: 429/501/656 nm

LBNL 2k x 4k CCD: Blue: H-α at 656 nm

Green: SIII at 955 nm Red: 1.02 µm

Planetary Nebula NGC 6853 (M 27) - VLT UT1+FORS1

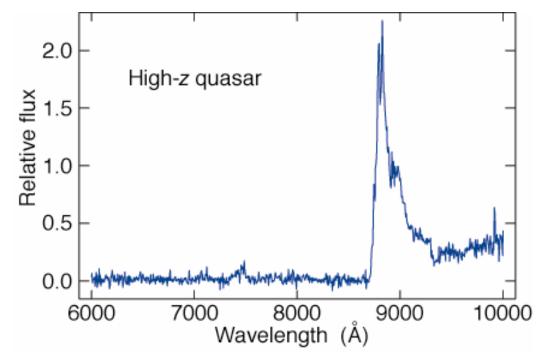

#### **Near infrared imaging and spectroscopy**

LNBL 1980 x 800 CCD: z > 6 Quasar spectrum NOAO Multi-aperture Red Spectograph

Data courtesy of Xiaohui Fan, University of Arizona Astronomy Department and the Sloan Digital Sky Survey, and Arjun Dey of the National Optical Astronomy Observatory

LBNL 2k x 4k CCD: Blue: H-α at 656 nm

Green: SIII at 955 nm Red: 1.02 µm

#### **Quantum efficiency**

At blue wavelengths the absorption length is very small, e.g.  $\sim 0.1~\mu m$  at 400 nm Requires a thin entrance window for high quantum efficiency

#### **Quantum Efficiency Measurements**

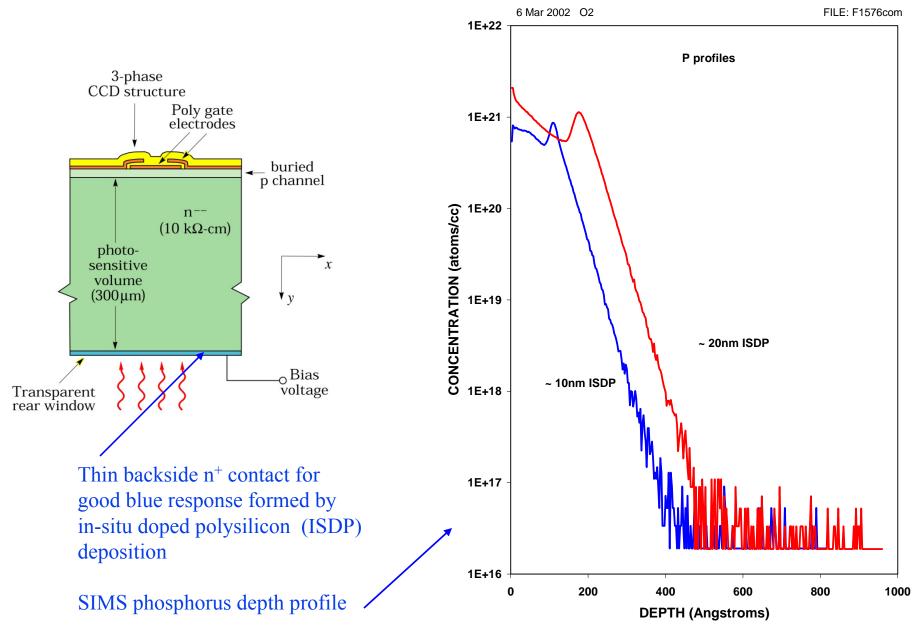

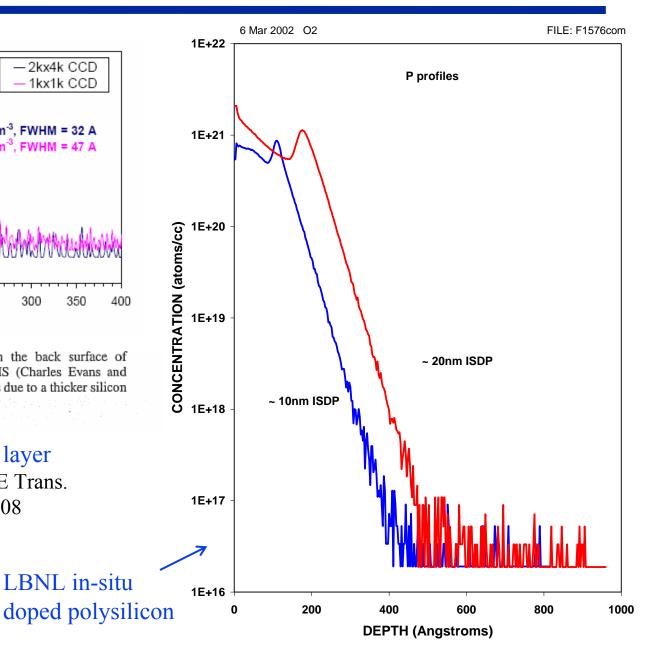

#### Thin backside n<sup>+</sup> ohmic contact development

#### Thin backside n<sup>+</sup> ohmic contact development

Fig. 1. Antimony concentration versus depth from the back surface of 1 k × 1 k and 2 k × 4 k CCDs obtained by SIMS (Charles Evans and Associates). The broader peak for the 1 k × 1 k CCD is due to a thicker silicon cap layer.

#### JPL MBE backside layer

J. Blacksberg et al, IEEE Trans. Elec. Dev., 55, 3402, 2008

LBNL in-situ

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

In thick, fully depleted CCDs the photogenerated holes must travel relatively large distances to the collection wells

The fully depleted substrate provides a drift electric field to reduce the transverse diffusion of carriers that results in degradation of spatial resolution

Thinned CCDs often have an undepleted, i.e field-free region that dominates the spatial resolution

One can show that the rms point spread function for carrier diffusion in a region without an electric field is equal to the thickness of the field-free layer

Start with the Crowell-Labuda modulation-transfer function expression derived for back-illuminated diode arrays used in the Bell Labs "Picturephone®"

M. Crowell and E. Labuda, "The silicon diode array camera tube," *Bell. Syst. Tech. J.*, **48**, 1481, 1969.

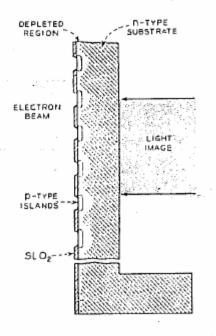

#### The Silicon Diode Array Camera Tube

By MERTON H. CROWELL and EDWARD F. LABUDA

(Manuscript received November 26, 1968).

A new electronic camera tube has been developed for Picturephone<sup>®</sup> visual telephone applications; with minor modifications it showld also be suitable for conventional television systems. The image sensing target of the new camera consists of a planar array of reversed biased silicon photodiodes which are accessed by a low energy scanning electron beam similar to that used in a conventional vidicon. This paper presents a description of the operating principles and an analysis of the sensitivity and resolution capabilities of the new silicon diode array camera tube.

We also give the detailed experimental results obtained with the tubes. The gamma of a silicon diode array camera tube is unity and its spectral response is virtually uniform over the wavelength range from 0.45 to 0.90 micron with an effective quantum yield greater than 50 percent. For a 13.4 millimeter square target the silicon diode array camera tube's sensitivity is 20 pamp foot-candles of faceplate illumination with normal incandescent illumination or 1.3 pamp per foot-candle with fluorescent illumination; with a center-to-center diode spacing of 15 micron it's modulation transfer function is greater than 60 percent for a spatial frequency of 14 cycles per millimeter. Typical dark currents for a 13.4 millimeter square larget are in the range of 5 to 50 nanoamperes.

ELECTRONIO CAMERA TUBE

1487

1484 THE BELL SYSTEM TECHNICAL JOURNAL, MAY-JUNE 19

Fig. 2 — Schematic of a diode array target. To obtain a self-supportiture, the perimeter of the wafer is left much thicker than the substrater of the diode array.

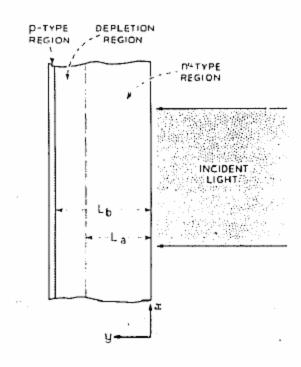

Fig. 3 — Schematic of the simplified model used to estimate the light sensitivity and resolving ability of a diode array target.

Crowell and Labuda back-illuminated photodiode array for the Picturephone®

Not fully depleted

Crowell and Labuda solved the continuity equation for the back-illuminated photodiode array with a sinusoidally varying light input to get the MTF

Neglecting recombination and assuming the light is absorbed in a distance small compared to the field-free region thickness results in an approximate MTF given by

$$MTF_{ff} \approx \frac{1}{\cosh(kL_{ff})}$$

Where  $k = 2\pi/\text{spatial period of the incident light}$

This expression was apparently well known to developers of back-illuminated infrared detectors

The point-spread function is the inverse Fourier transform of the modulation-transfer function, i.e.

$$PSF_{ff} = \frac{1}{2L_{ff} \cosh\left[\frac{\pi x}{2L_{ff}}\right]}$$

The rms width of the PSF from the Moment Theorem is

$$\sigma = L_{ff}$$

Key point: Partially depleted, back-illuminated imagers can have a spatial resolution that is dominated by the thickness of the field-free layer

#### **Point Spread Function: Simplified Model**

- Fully depleted CCD: Point spread function (PSF) is determined by the hole transit time in the electric field

- For carriers with the same arrival time at the CCD potential wells, the distribution is Gaussian

Constant field approximation (simplified model)

$$\sigma = \sqrt{2D_p t_{tr}}$$

$$t_{tr} = \frac{z_{sub}}{v} = \frac{z_{sub}}{\mu_p E} = \frac{z_{sub}}{\mu_p (V_{sub} - V_J)}$$

$$D_p / \mu_p = kT / q$$

$$D_p / \mu_p = kT / q \qquad \sigma = z_{sub} \sqrt{\frac{kT}{q} \frac{2}{(V_{sub} - V_J)}}$$

$Z_{sub}$  ~ Thickness of CCD

kT/q Thermal voltage

$V_{sub} - V_I$  Voltage across drift region

### **Point Spread Function Issues**

Long dark images (30 minute integrations) showing background radiation events from Compton electrons and cosmic rays

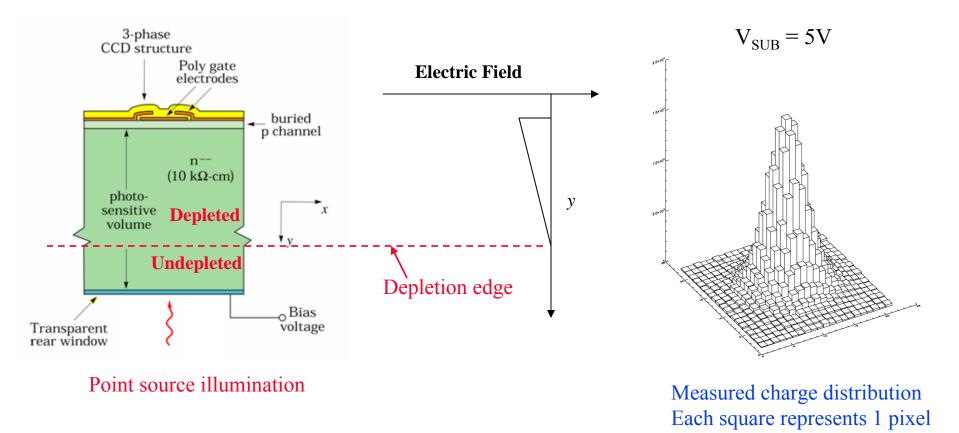

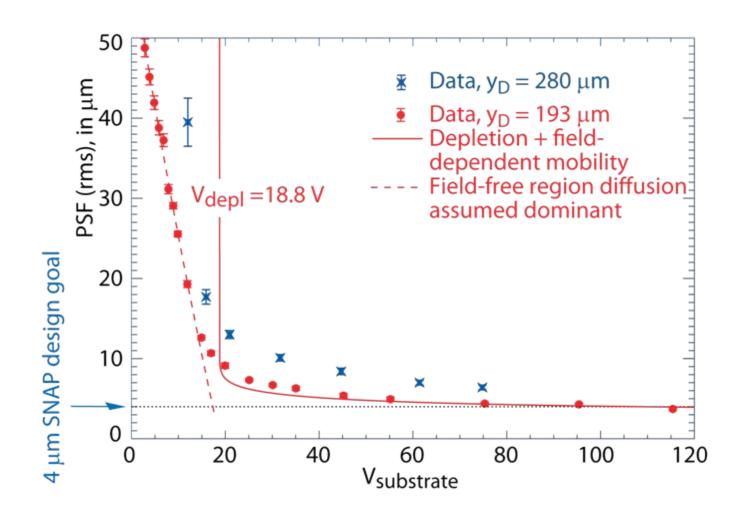

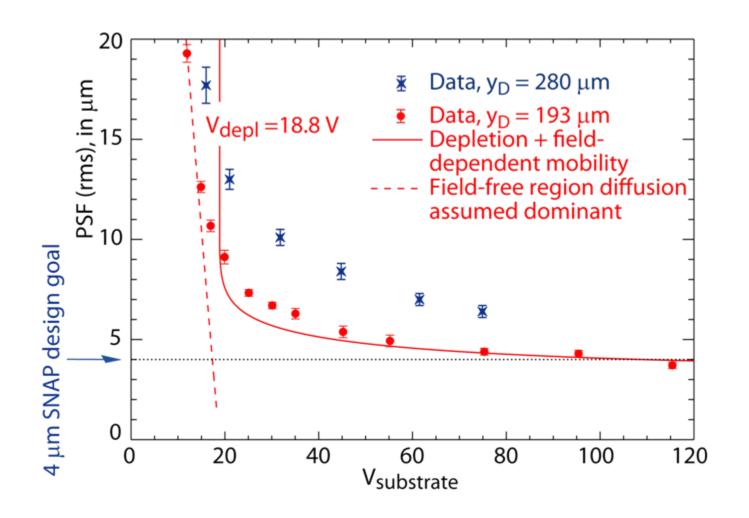

#### **Spatial resolution: Effect of substrate voltage**

At low substrate bias voltages the CCD is not fully depleted

The PSF is dominated by diffusion in the undepleted silicon

Can be shown that  $\sigma$  ~ the field-free region thickness

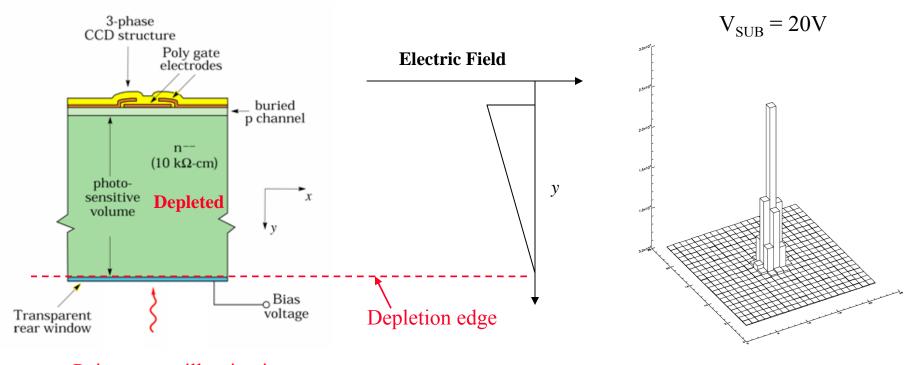

# **Spatial resolution: Effect of substrate voltage**

Point source illumination

Measured charge distribution Each square represents 1 pixel

At 20V the CCD corresponding to the data is just fully depleted

The PSF is limited by the transit time of the photogenerated holes

$$\sigma = \sqrt{2Dt_{tr}}$$

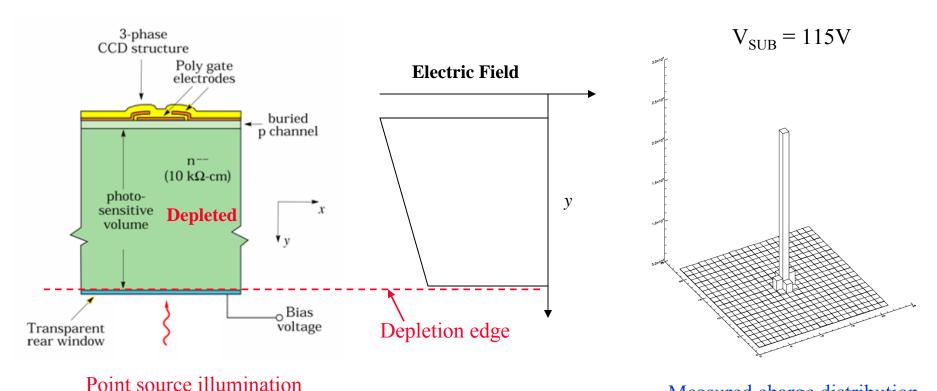

# **Spatial resolution: Effect of substrate voltage**

Measured charge distribution Each square represents 1 pixel

The PSF continues to improve (but slowly) as  $V_{SUB}$  in increased

At  $V_{SUB}$ =115V the rms diffusion for this 200  $\mu$ m thick, 10.5  $\mu$ m pixel CCD is 3.7  $\pm$  0.2  $\mu$ m

#### PSF measurements on 200 and 280 µm thick CCDs

Need to include the electric field dependence of hole mobility for good fits at high voltage (J. Fairfield et al, IEEE Trans. Nucl. Sci., **53**, 3877, 2006)

#### PSF measurements on 200 and 280 µm thick CCDs

Need to include the electric field dependence of hole mobility for good fits at high voltage (J. Fairfield et al, IEEE Trans. Nucl. Sci., **53**, 3877, 2006)

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

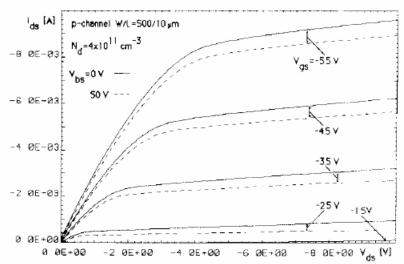

# Transistors on high-resistivity silicon

- Vanstraelen *et al* of IMEC demonstrated the utility of the substrate bias voltage in suppressing punchthrough currents for p-channel transistors fabricated directly on high resistivity silicon

- High energy physics applications

- G. Vanstraelen, I. Debusschere, C. Claeys, and G. Declerck, *Nucl. Instrum. Meth. In Phys. Res. A*, **273**, 625, 1988

- Due to the extremely low substrate doping the body effect is quite small, resulting in small threshold voltage changes for large changes in  $V_{\text{sub}}$

- Nonetheless, the channel length is limited by the punchthrough characteristics to about  $2-3 \mu m$

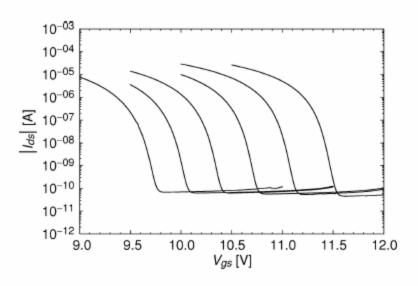

# Transistors on high-resistivity silicon cont'

Fig. 9.  $I_{\rm ds}(V_{\rm gs}) - V_{\rm ds}$  characteristics of the 10  $\mu$ m device. Solid lines:  $V_{\rm bs} = 0$  V; dashed lines:  $V_{\rm bs} = 50$  V.

500/10 P-channel MOSFET (surface channel) 10 k $\Omega$ -cm substrate (n type)

G. Vanstraelen, I. Debusschere, C. Claeys, and G. Declerck, *Nucl. Instrum. Meth. In Phys. Res. A*, **273**, 625, 1988.

Fig. 8. Measured subthreshold characteristics of a 47/6 buried channel PMOSFET with 1.5- $\mu$ m gate-to-source/drain spacing. The substrate bias varied from 25 (rightmost curve) to 75 V (leftmost curve) in 10-V steps. The temperature was -128 °C, and the drain to source voltage was -1 V.

47/6 P-channel MOSFET (buried channel) 10 k $\Omega$ -cm substrate (n type)

Source-follower transistor used on LBNL CCDs

S.E. Holland, D.E. Groom, N.P. Palaio, R.J. Stover and M. Wei, *IEEE Trans. Elec. Dev.*, **50**, 225, 2003.

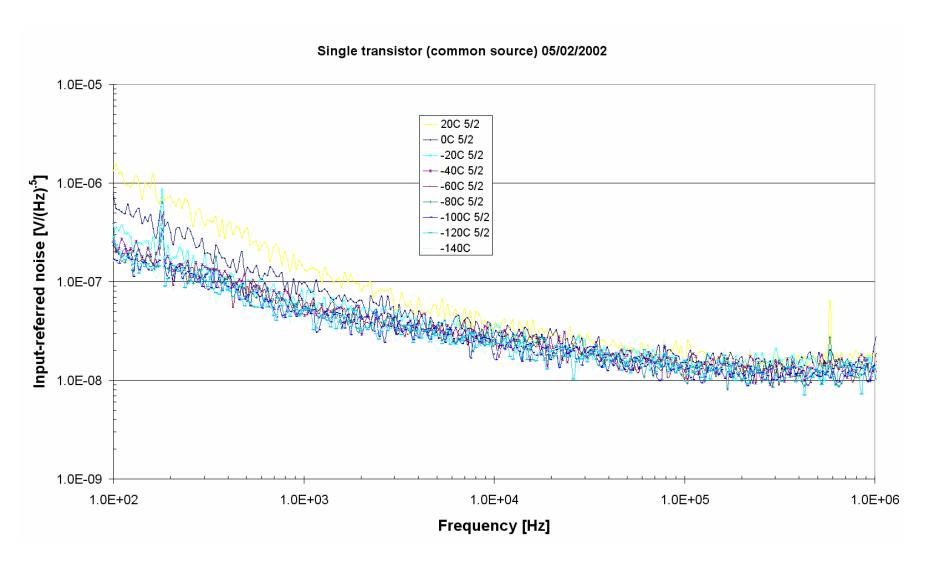

# **Noise measurements (20C to -140C)**

47/6 buried channel P MOSFET: White noise  $\sim 10 \text{ nV/Hz}^{1/2}$

# Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

#### CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

## Summary

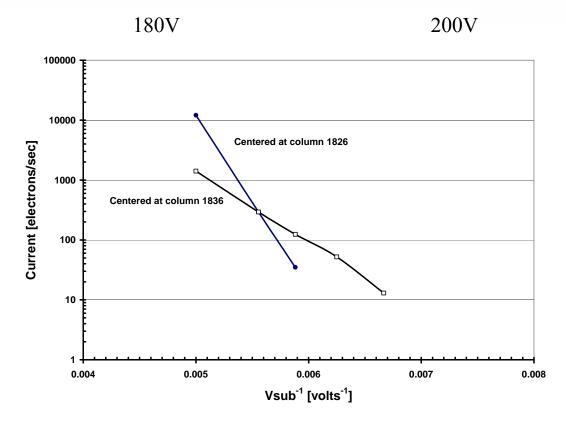

# Fully depleted CCDs: Backside defects

Overdepleted operation results in a significant electric field at the backside of the CCD

Defects at the back side of the CCD can result in high dark current

# **High-voltage considerations: Dark current from backside defects**

$$V_{sub} = 160V$$

Sub-image: 290 x 220 pixels

Temperature = -140C

CCD 107409-22-3 1700 x 1836 (10.5 µm pixel)

200 µm thick CCD

# **High-voltage considerations: Dark current from backside defects**

Temperature = -140C

-120C

-105C

Sub-image: 290 x 220 pixels  $V_{sub} = 170V$

CCD 107409-22-3 1700 x 1836 (10.5 µm pixel)

200 µm thick CCD

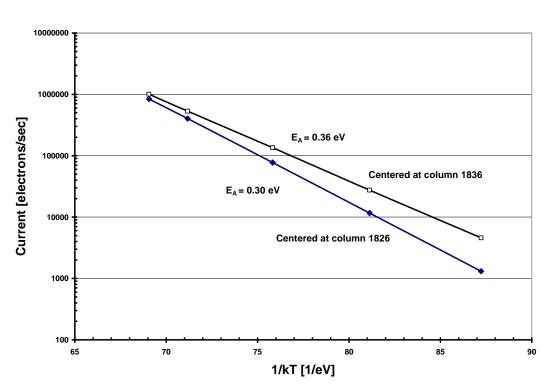

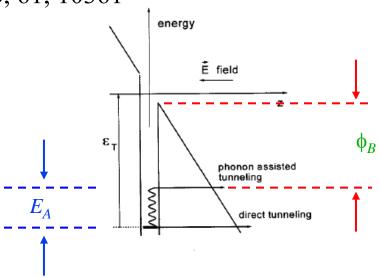

# Trap-assisted tunneling: Dark current issue with fully depleted CCDs

Phys Rev B, 61, 10361

WKB tunneling factor:

$$\exp\left(-\frac{4\sqrt{2}}{3}\frac{m_r^{1/2}\phi_B^{3/2}}{e\hbar E}\right)$$

Boltzmann factor:  $\exp(-E_A/kT)$

$$E_{BACK} = -\left(\frac{V_{sub} - V_{J}}{y_{sub}} - \frac{qN_{D,sub}}{\varepsilon_{Si}}y_{sub}\right)$$

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

- We use a hybrid fabrication approach to CCD production

- —Most of the processing is done at DALSA Semiconductor, a commercial foundry located in Bromont, Quebec, Canada

- We use a hybrid fabrication approach to CCD production

- —Most of the processing is done at DALSA Semiconductor, a commercial foundry located in Bromont, Quebec, Canada

www.dalsa.com

2.5 µm CCD technology with scanner lithography for large-area CCD fabrication 150 mm diameter wafers

- Hybrid fabrication approach to CCD production (cont')

- —The wafers are shipped to LBNL after completion of about 80% of the processing

- —The wafers are thinned to the final desired thickness, typically 200–250 μm thick, at a commercial vendor

- Process is backgrind followed by CMP to remove subsurface damage introduced by the backgrind

- —Processing of thinned wafers at the foundry is not feasible at this time, so the specialized steps on thinned wafers are done at LBNL

- Hybrid fabrication approach to CCD production (cont')

- —The wafers are then completed for back-illumination at the LBNL MicroSystems Laboratory

- Backside in-situ doped polysilicon deposition

- Conventional contact/metal lithography and etch

- Backside anti-reflection coatings

- -55 nm ITO, 80 nm SiO<sub>2</sub>

- —The processing is done in <u>batch mode at the wafer level</u> using conventional semiconductor fabrication equipment, with some modifications to the equipment to avoid backside damage during robotic wafer handling

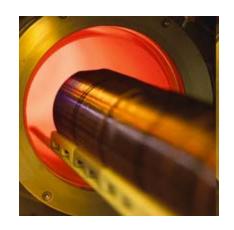

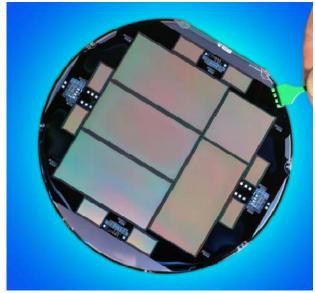

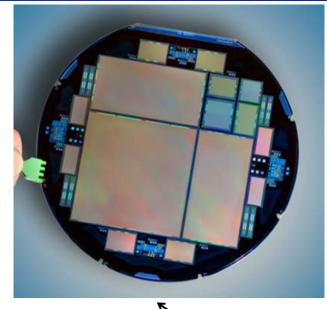

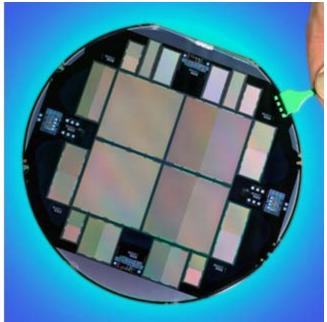

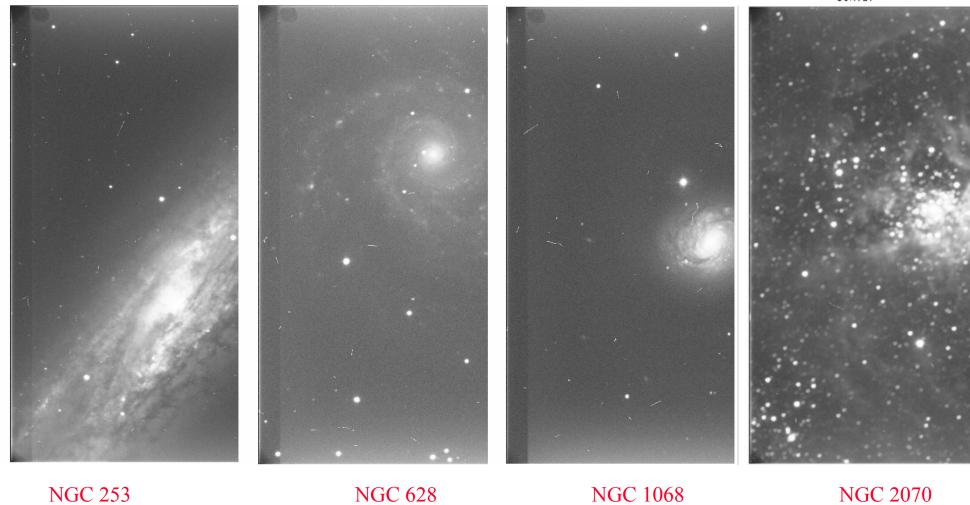

# Current LBNL CCD efforts on 150 mm diameter wafers with DALSA Semiconductor

Dark Energy Survey camera wafer (FNAL)

62 2k x 4k CCDs required for a camera at CTIO telescope in Chile

4k x 4k wafer

Sloan/Keck spectrograph upgrades and SWIFT spectrograph (Palomar)

SNAP V3 wafer

JDEM (space mission) candidate

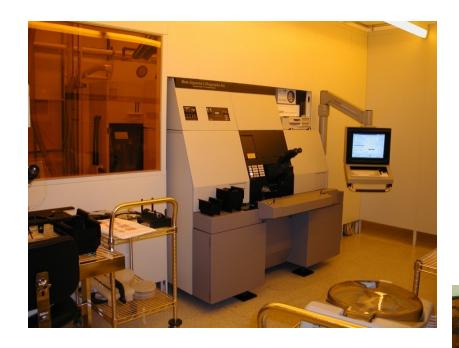

# LBNL MicroSystems Laboratory

- Class 10 semiconductor fabrication facility

- —Upgraded to 150 mm wafer capability

Projection aligner lithography system Beta Squared Lithography (P/E)

> Dielectric plasma etcher Lam 4520 XLE

Atmospheric and low pressure chemical vapor deposition furnaces Expertech (Thermco)

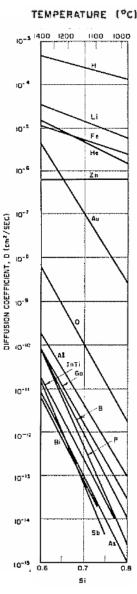

Need to maintain the high resistivity of the wafers throughout the high-temperature processing steps used in CCD fabrication

• Also need to eliminate metallic contamination that can affect dark current and charge transfer efficiency

—Gettering steps required

# Gettering for high-resistivity silicon

From S. M. Sze, "Physics of Semiconductors Devices", 2<sup>nd</sup> edition, 1969.

- Metal contamination in silicon results in energy levels in the silicon bandgap, resulting in increased dark current and carrier trapping

- However, the metals are fast diffusers and can be trapped at gettering sites

- We begin CCD processing by depositing a 1 μm thick, in-situ doped (phosphorus) polysilicon (ISDP) layer on the backside of the wafer

- Metals trapped in polysilicon grain boundaries and by P-vacancy complexes

# **Gettering details**

- The in-situ doped polysilicon gettering layer is not a standard process from the vendors of high-resistivity silicon wafers, so this step is done at DALSA Semiconductor

- We have observed metal contamination from robotic wafer handlers that contact the wafer before the gettering layer is deposited

- —Process flow has been modified to avoid this condition

• The polysilicon deposition process is inherently "dirty", and we repolish the front sides of the wafers to remove particles deposited during the long deposition step

# **Gettering issues: ISDP particles**

Particle map after ISDP deposition

Particle map/histogram after polishing

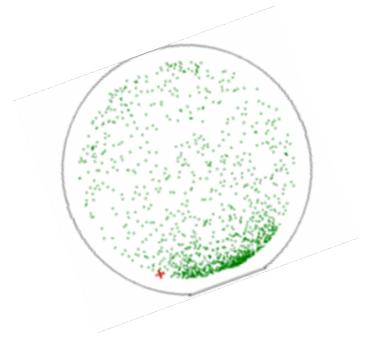

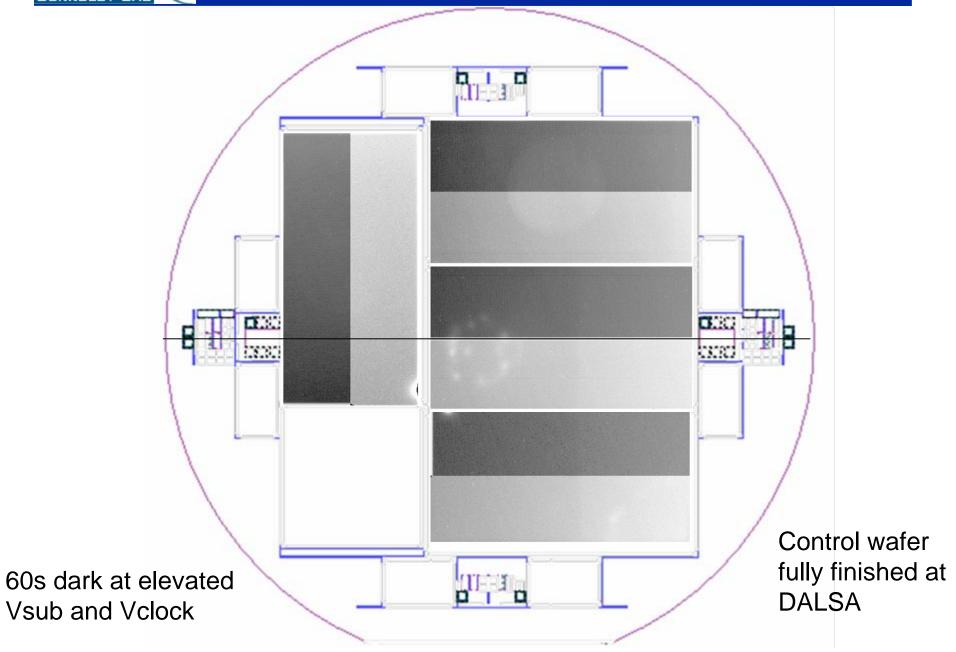

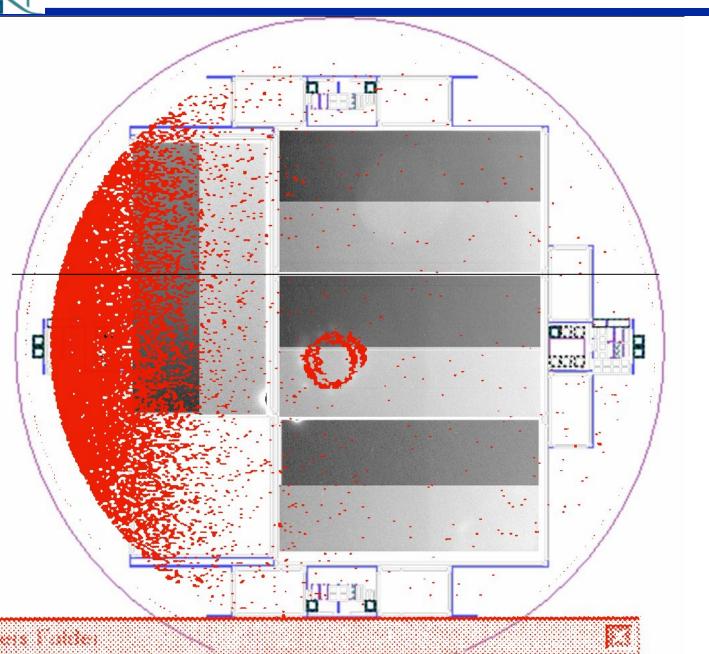

### Cold probe image (-45C) map of FNAL DES wafer

#### Overlay of particle map on cold probe images

Red: Particle map supplied by DALSA

The source of the particles are robotic handlers that come in contact with the back sides of the wafers

#### Cold probe result on 4k x 4k with new process flow

127298-1 60 sec dark -45C cold probing DALSA control wafer

Elevated Vsub and Vclock

New lot with modified process flow to eliminate contamination seen on previous 4k x 4k lot

#### COLD PROBE SUMMARY

Device: 127298.1.4

Format: SNAP, 4 corner readout Test Date: 2008-08-26T11:55:08.000

Temperature: -45C. Operator Initials: JE.

#### 1. Summary of Bad Columns

No hot columns in 1 s dark image.

No hot columns introduced by increasing clock voltages.

No hot columns introduced by increasing Vsub.

No blockedcolumns.

There are no bad columns in this device

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

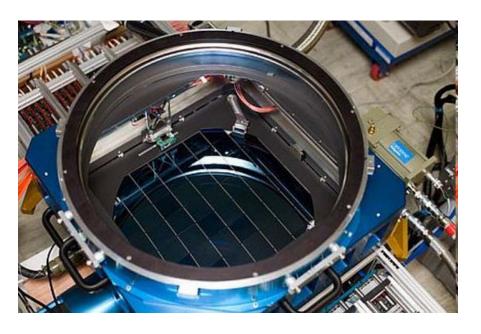

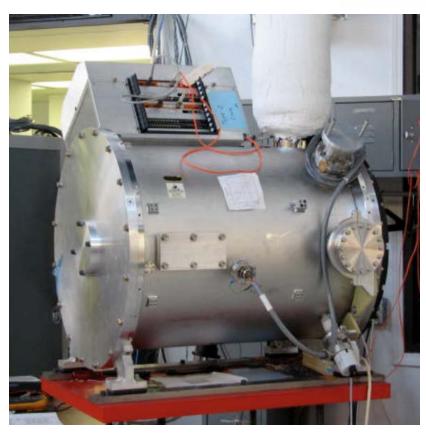

#### **Dark Energy Survey Camera (FNAL)**

LBNL provides cold probed die

Packaging and final testing done at FNAL

The camera requires

62 science-grade,

2k x 4k (15 µm pixel)

CCDs

The camera will be installed at CTIO

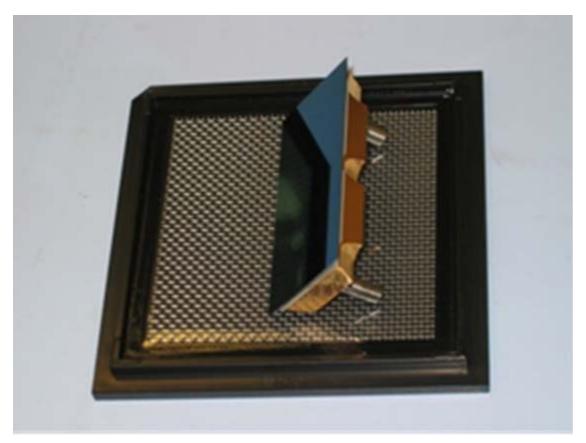

2k x 4k CCD in FNAL 4-side buttable package

Image courtesy of T. Diehl (FNAL)

#### **Dark Energy Survey efforts at FNAL**

FNAL multi-CCD test vessel: Currently reading out 12 engineering grade CCDs

Picture on the right shows a Monsoon crate with high-density boards developed by collaborators from Spain

# **Dark Energy Survey efforts at FNAL**

# Pin hole image

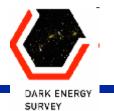

## **Dark Energy Survey Camera (FNAL)**

Crab Nebula 10/3/2008

2k x 2k from CTIO 1-m telescope *Image courtesy of D. Kubik (FNAL)*

10/3/2008

## **Dark Energy Survey Camera (FNAL)**

2k x 1k images from CTIO 1-m telescope *Images courtesy of D. Kubik (FNAL)*

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

# 4k x 4k development

- We are fabricating 4k x 4k (15 μm pixel) CCDs for ground-based spectroscopy

- —Baryon Oscillation Spectroscopic Survey (BOSS) at Sloan

- —Possible Keck LRIS upgrade

Have also delivered 4k x 2k (15 μm pixel) CCDs for SWIFT (Palomar)

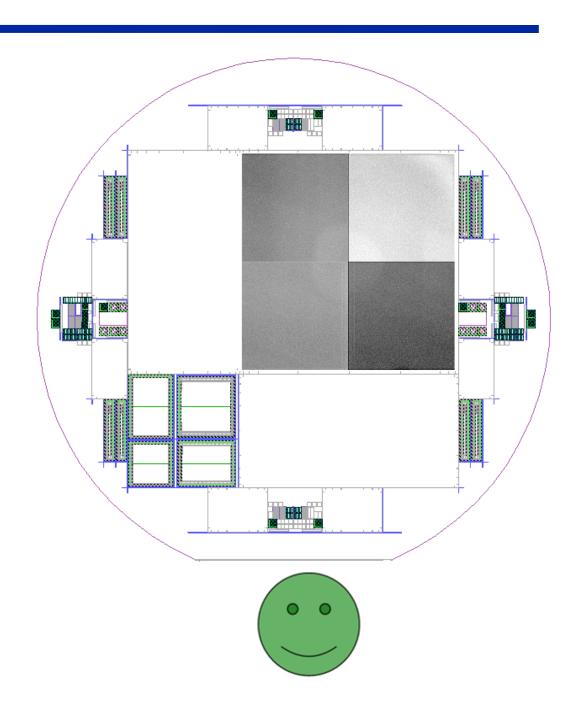

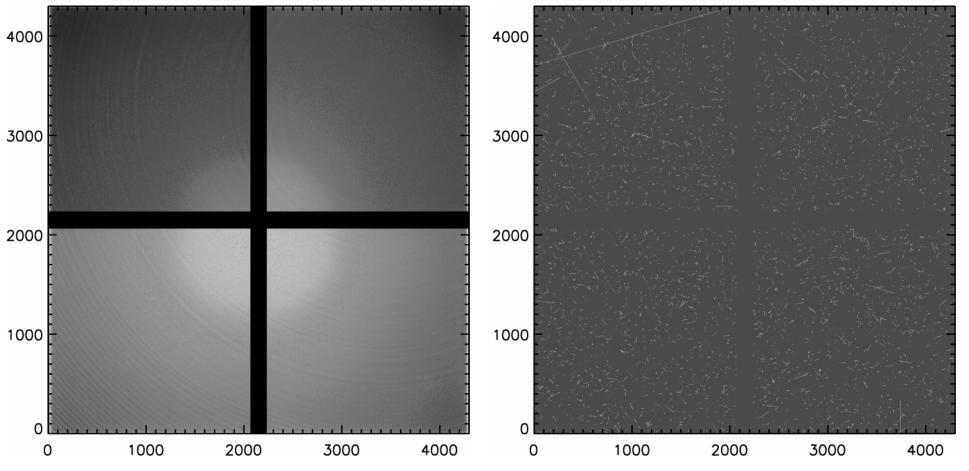

# Packaged 4k x 4k at -140C with new process flow and after LBNL backside defect yield improvement

Flat field image (slightly non-uniform light source)

Dark current (30 minute exposure) 0.7 electrons/pixel-hour at -140C

Science-grade CCD to be installed at the Sloan Digital Sky Survey telescope

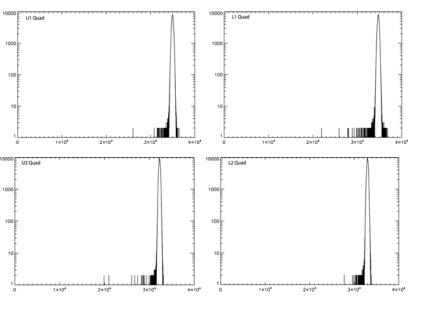

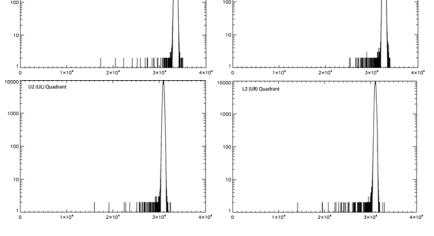

#### Test summaries for BOSS 4k x 4k's

| Transistor | Gain (ADU/e-) | Noise (e-) |

|------------|---------------|------------|

| U1(LL)     | 1.569         | 3.0        |

| U2(UL)     | 1.450         | 3.1        |

| L1(LR)     | 1.566         | 2.9        |

| L2(UR)     | 1.499         | 3.3        |

| Observed Traps with Depth 50% or more |               |               |              |  |  |

|---------------------------------------|---------------|---------------|--------------|--|--|

| Quadrant                              | Forward Traps | Reverse Traps | Trap Density |  |  |

| U1 (LL)                               | 59            | 23            | 2.11E-05     |  |  |

| L1 (LR)                               | 59            | 18            | 1.98E-05     |  |  |

| U2 (UL)                               | 44            | 39            | 2.14E-05     |  |  |

| L2 (UR)                               | 33            | 28            | 1.57E-05     |  |  |

| Transistor | Gain (ADU/e-) | Noise (e-) |

|------------|---------------|------------|

| U1(LL)     | 1.556         | 3.4        |

| U2(UL)     | 1.468         | 3.2        |

| L1(LR)     | 1.525         | 4.0        |

| L2(UR)     | 1.385         | 3.5        |

| Observed Traps with Depth 50% or more |               |               |              |  |  |  |

|---------------------------------------|---------------|---------------|--------------|--|--|--|

| Quadrant                              | Forward Traps | Reverse Traps | Trap Density |  |  |  |

| U1 (LL)                               | 122           | 97            | 5.64E-05     |  |  |  |

| L1 (LR)                               | 90            | 58            | 3.81E-05     |  |  |  |

| U2 (UL)                               | 118           | 83            | 5.18E-05     |  |  |  |

| L2 (UR)                               | 95            | 86            | 4.66E-05     |  |  |  |

Flat Field Histograms U1 (LL) Quadrant

127298-14-4: 0.7 e-/pixel-hr at -140C

0 hot columns0 hot pixels5 dark pixels

Hot/dark pixels exceed 20% from median

127298-8-4: 0.7 e-/pixel-hr at -140C

2 "warm" columns 0 blocked columns

1 hot pixels 29 dark pixels

Hot/dark pixels exceed 20% from median

- Fully depleted CCD physics and performance

- Quantum efficiency and fringing

- Spatial resolution

- Transistors fabricated on high-resistivity silicon

- Backside defects

- CCD fabrication

- Hybrid fabrication model

- Dark Energy Survey project

- 4k x 4k (15 μm pixel) development

- Summary

- Fully depleted operation is preferable in order to maintain good spatial resolution for back-illuminated CCDs

- This puts stringent demands on the backside layer

- —Hot pixels can result when the depletion region reaches the back surface

- —For scientific CCDs used in astronomy, cryogenic operation greatly reduces the effect

- —Backside layer is critical

- ISDP works well but is not compatible with aluminum metallization

- For our application we are able to process 200–250 μm thick wafers with standard semiconductor fabrication equipment, allowing for batch-mode fabrication

- Much effort has gone into the fabrication model used at LBNL, but the process is now fairly routine and stable

- Thinning technology development

- Low damage plasma etch development

- Gettering issues

- Robotic wafer handling to minimize backside damage

- We look forward to commercially available, back-illuminated imagers

# Acknowledgements

- LBNL CCD group: N. Roe (Group leader), C. Bebek, J. Emes, D. Groom, A. Karcher, W. Kolbe, J. Lee, N. Mostek, N. Palaio, J. Thacker, C. Tran, G. Wang

- Lick Observatory: W. Brown, R. Stover, M. Wei

- FNAL DES group: T. Diehl, J. Estrada, B. Flaugher, D. Kubik

- JPL: S. Nikzad, J. Blacksberg, M. Hoenk, S. T. Elliott

- DALSA Semiconductor: R. Groulx, F. Dion

- References: http://www-ccd.lbl.gov