# 9.8µm SPAD-based Analogue Single Photon Counting Pixel with Bias Controlled Sensitivity

Neale A.W. Dutton<sup>1,2</sup>, Lindsay A. Grant<sup>1</sup>, Robert K. Henderson<sup>2</sup>

1. ST Microelectronics Imaging Division, Pinkhill, Edinburgh, EH12 7BF, UK 2. The University of Edinburgh, Edinburgh, EH9 3JL, UK

Web: www.css.eng.ed.ac.uk

Email: neale.dutton@st.com

Tel: +44 (0)131 650 5658 / +44 (0)131 336 6170

Abstract: A scalable NMOS-only 11T SPAD-based analogue single photon counting pixel is presented. Implemented in advanced 130nm imaging low voltage CMOS, with no extra implants, a state of the art 9.8µm pitch is achieved. Novel pixel operation using a charge transfer amplifier (CTA) allows bias controlled sensitivity from 13.1mV/event 150µV/event. Less than 2% PRNU is measured in the sensitivity range 5.5mV to 13.1mV per event with <0.01e input referred noise. A second mode operates the CTA as a switched current source enables the pixel to operate as a fast time-gated Quanta Image Sensor pixel.

### I. INTRODUCTION

ingle photon counting (SPC) image sensors have a number of applications such as time-of-flight (TOF) ranging and advanced microscopy [1][2][3]. CMOS single photon avalanche diode (SPAD) based image sensors offer the combined advantage of integration of electronics and high timing precision. In CMOS SPAD-based pixels, a trade-off exists between pixel pitch, fill factor and in-pixel functionality. Henderson et al. [4] have presented the smallest reported pitch of 5µm using minimal in-pixel circuitry. Higher fill factor is achieved by [1] and [5] by placing the timing or counting circuitry outside the array, yet this puts a limitation on signal routing and increases bus-sharing affecting scalability to mega-pixel arrays. By comparison, Walker et al. [6] implemented a high degree of functionality using an all-digital pixel with a 44.65µm pitch at the cost of 3.2% fill factor. A good compromise was reached by Pancheri et al. [3], who utilised an analogue SPC within 25µm pitch with 21% fill factor. However, in that work the current consumption of the NMOS-only inverter limits integration into a large array. The pixel proposed by Panina [7] has a high transistor count, and adding PMOS devices increases the pitch because of N-Well spacing rules. The NMOS-only SPC proposed by Chitnis [8] uses the SPAD 'on' time to control a current discharge with the disadvantage that the voltage step is quench voltage and dead-time dependent.

In this paper, we present a NMOS-only, zero static bias current, 11T SPAD-based analogue SPC pixel in 130nm

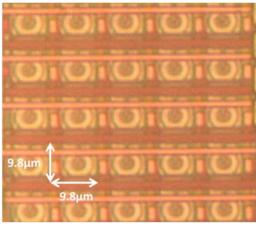

Fig.1 Photomicrograph of the SPC Test Array

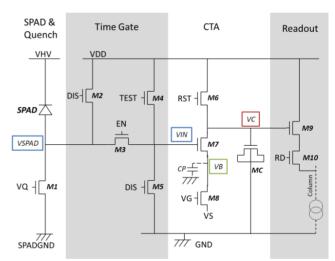

Fig.2 Pixel Schematic

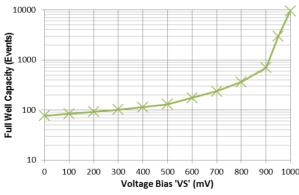

low voltage CMOS with no extra implants. We achieve a state of the art  $9.8\mu m$  pixel pitch for a SPC SPAD pixel, which is scalable to large arrays. We demonstrate novel and versatile pixel operation utilising a charge transfer amplifier (CTA) to produce a variable voltage step, allowing voltage controllable sensitivity from 1.08V/event to  $150\mu V/event$ , and hence electrically adjustable full well capacity from 1 to 1,000 events.

## II. SPC PIXEL

A photomicrograph of the 3x3 SPC test array, with surrounding dummy pixels, is displayed in Fig.1. The SPAD is a modified P-Well to deep N-Well structure from [9] with a  $2\mu m$  diameter anode and a reduced guard ring to facilitate the sub- $10\mu m$  pitch. It has 99Hz

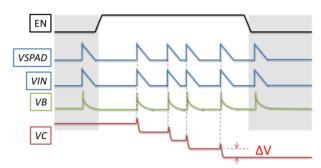

Fig.3. CTA Timing Illustration

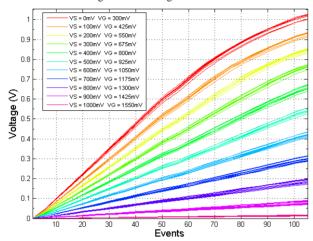

Fig.4. Emulation of 9 Pixels in CTA Mode – 1 to 100 Events

median dark count rate (DCR). The pixel has a 3% fill factor with the single isolated SPAD and compact surrounding electronics. The schematic is shown in Fig. 2. It consists of four parts: SPAD and quench, time gate, CTA and standard APS-based readout. To realise SPC operation with controllable sensitivity the pixel is operated in two distinct modes. The first operates the pixel as a CTA: It functions by transferring charge from the capacitor MC (17fF) to the parasitic capacitance C<sub>P</sub> (~0.1fF) at node V<sub>B</sub>. This operation is achieved by biasing M8 in sub-threshold, with M8 acting as a high valued resistance. CTAs derive from low-power A/D converters [10]. Fig. 3 illustrates the CTA mode timing. The second mode operates the CTA as a switched current source (SCS), with M8 above threshold, enabling fast single photon detection.

In CTA mode, the magnitude of the voltage step ' $\Delta V$ ' is determined by the capacitance ratio and the  $V_{GS}$  of the dynamic source follower M7 (formed by the input voltage  $V_{IN}$  and by  $V_{B}$ ). The step size ( $\Delta V$ ) is therefore bias adjustable:

$$\Delta V = (\Delta V_{IN} - V_S - V_T) \cdot (C_P/C_{MC})$$

(1)

The ' $V_S$ ' bias allows the control of the step size and the ' $V_G$ ' bias is used to compensate for the body effect on the threshold voltage, which is estimated in the characterisation. The pixel response characteristic, in CTA mode, is emulated by using the M4 test transistor.

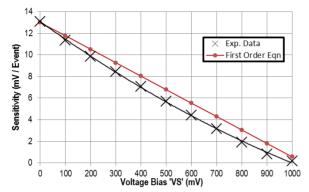

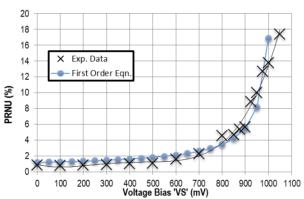

An example of an emulated graph is shown in Fig. 4. Both the emulation and SPAD mode use a high voltage, on the gates of M4 or M3 respectively, to reduce the relative contributions of their V<sub>T</sub> variability. As shown in equation (1), the pixel sensitivity is dependent on the source bias voltage 'Vs' and this relationship is displayed in Fig.6. The first order equation (1) has been fitted to Fig.6 to confirm the CTA operation ( $\Delta V_{IN}$  is assumed to be a constant value and an approximation from simulation is made for parameters V<sub>T</sub> and (C<sub>P</sub>/C<sub>MC</sub>)). The pixel response non-uniformity (PRNU) is proportional to the variability of each voltage step. Therefore operating with lower sensitivity, the step variability is a higher proportion of the step magnitude. The PRNU is expressed in equation (2) where  $V_P$  is the counter output peak voltage after CDS, N is the full well capacity,  $\sigma_{\Delta V}$  is the std. deviation of the voltage step variability and  $\sigma_I$  represents the noise contribution from other sources independent of 'Vs' bias (e.g. read and ADC noise during readout). Equations (3.1) and (3.2) shows the std. deviation  $\sigma_{\Delta V}$  under different inputs assuming the source follower gain is unity, where  $(\sigma_{VSPAD})^2$  is the variance of the SPAD during avalanche and  $(\sigma_{VT M7})^2$  is the variance of the  $V_T$  of the source follower M7.

PRNU =

$$\sqrt{\left(\frac{\sigma_{\Delta V} \cdot N}{Vp}\right)^2 + (\sigma_I)^2}$$

PRNU =

$$\sqrt{\left(\frac{\sigma_{\Delta V}}{\Delta V}\right)^2 + (\sigma_I)^2}$$

(2)

With SPAD input:

$$\sigma_{\Delta V} = \left(\frac{c_P}{c_{MC}}\right) \cdot \sqrt{\left(\sigma_{VT\_M7}\right)^2 + \left(\sigma_{VSPAD}\right)^2} \quad (3.1)$$

With emulation input:

$$\sigma_{\Delta V} = \left(\frac{c_P}{c_{MC}}\right) . \sigma_{VT\_M7} \quad (3.2)$$

Equation (2) is fitted using the same parameters as Fig. 6 and plotted against measured PRNU values in Fig. 7.

# III. RESULTS

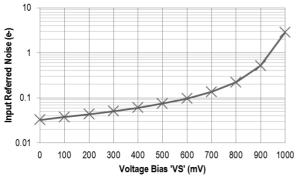

The 3x3 array has an analogue column output connected to a 14b external ADC for characterisation. Correlated multiple sampling (CMS) is used to sample the analogue output, as shown in Fig. 5, with 4096 samples before and after integration to suppress reset noise. The ADC noise contribution is evaluated at  $426\mu V$  RMS by tying the inputs together to a mid-rail bias. This ADC noise is dominant in our experimental setup, which masks the output source follower M9 noise contribution (RTS, 1/f and thermal) and the kT/C noise of the inpixel capacitance  $C_{MC}$ .

Fig.5. Correlated Multiple Sampling Timing Diagram

Fig.6. Pixel Sensitivity versus Voltage Bias 'Vs'

Fig.7. Pixel Response Non-Uniformity versus Voltage Bias 'Vs'

Fig.8. Full Well Capacity versus Voltage Bias 'Vs'

Fig.9. Input Referred Noise versus Voltage Bias 'Vs'

The pixel sensitivity and full-well capacity were measured against a sweep of ' $V_S$ ' bias in CTA mode, and the PRNU and input referred noise were calculated. These results are plotted in figures 6 to 9. PRNU less than 2% is obtained in the range of ' $V_S$ ' bias 0mV to 600mV with corresponding sensitivity range 5.5mV to 13.1mV per event and input referred noise 0.03e $^-$  to 0.1e $^-$ . Greater dynamic range and lower sensitivity are obtainable at the cost of high PRNU and higher noise. The pixel variability rapidly degrades to 17.4% PRNU as ' $V_S$ ' bias is swept to 1V with 150  $\mu V$  per event sensitivity and 2.8e $^-$  input referred noise.

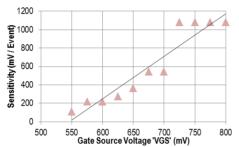

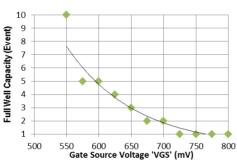

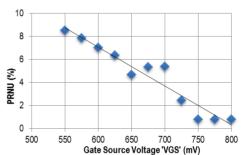

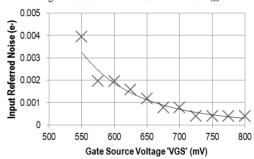

The SCS mode measurement results are included in figures 10 to 13. The sensitivity is measured with steps of 108mV/event to the full swing of 1.08V/event with corresponding full well of 10 to 1 events. The input referred noise across the same range varies from 0.004e to 0.0004e. High variability is evident in SCS mode, precluding accurate counting operation but instead offering coarse detection of zero, one or few photons. A pixel array implementation utilising high-speed readout would serve as a time-gated Quanta Image Sensor, proposed by Fossum in [11].

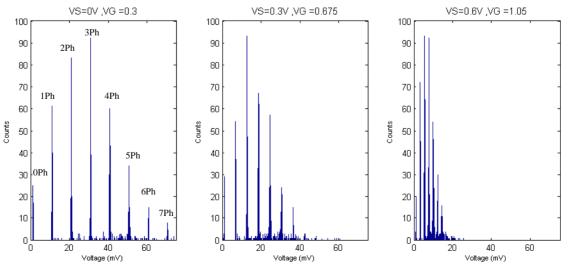

The pixels were tested under light with the SPADs enabled in CTA mode. Fig.14 demonstrates the discretised Poisson-distributed output voltage histogram from all pixels at varying bias under constant light, clearly illustrating the voltage step controllability.

## **CONCLUSION**

An 11T, NMOS-only SPAD-based SPC pixel is implemented in low voltage 130nm imaging CMOS with no extra implants. Charge transfer amplifier operation allows bias controlled sensitivity from 13.1 mV/event to  $150 \mu V/event$ . PRNU <2% is measured operating in the 'Vs' bias range from 0 to 600mV with sensitivities from 13.1 mV to 5.5 mV per photon and  $0.03 e^-$  to  $0.1 e^-$  input referred noise respectively. Higher 'Vs' bias increases the pixel dynamic range and decreases sensitivity at the cost of high PRNU. A second switched current source mode facilitates high-speed single photon detection. This pixel is scalable to large arrays offering high-resolution single photon imaging in the near future for TOF and advanced microscopy applications.

## **ACKNOWLEDGEMENTS**

The support and assistance in this work, of Mr David Poyner and Drs. Andrew Holmes, Sara Pellegrini, Bruce Rae and Richard Walker are gratefully acknowledged.

### REFERENCES

- Teranishi, N., "Required Conditions for Photon-Counting Image Sensors," Electron Devices, IEEE Transactions on, vol.59, no.8, pp.2199,2205, Aug. 2012

- [2] C. Niclass; M. Soga; H. Matsubara; S. Kato; , "A 100m-range 10-frame/s 340×96-pixel time-of-flight depth sensor in 0.18µm CMOS," ESSCIRC (ESSCIRC), 2011 Proceedings of the , pp.107-110

- [3] L. Pancheri; N. Massari; F. Borghetti; D. Stoppa; , "A 32x32 SPAD Pixel Array with Nanosecond Gating and Analog Readout" 2011, International Image Sensors Workshop (IISW) 2011, Proceedings of the, R40

- [4] R.K. Henderson et al., "A 3×3, 5µm pitch, 3-transistor single photon avalanche diode array with integrated 11V bias generation in 90nm CMOS technology," 2010, Electron Devices Meeting (IEDM), 2010 IEEE International, pp.14.2.1-14.2.4

- [5] R. J Walker. et al., "A 92k SPAD Time-Resolved Sensor in 0.13µm CIS Technology for PET/MRI Application", 2013, International Image Sensors Workshop (IISW), Proceedings of the.

- [6] R.J. Walker et al., "A 128×96 pixel event-driven phase-domain ΔΣ-based fully digital 3D camera in 0.13μm CMOS imaging technology", 2011, Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, pp.410-412

- [7] E. Panina; G. Dalla Betta; L. Pancheri; D. Stoppa;, "Design of CMOS Gated Analog Readout Circuits for SPAD Pixel Arrays" 2012, PRIME 2012, pp.39 to 42

- [8] D. Chitnis and S. Collins , "Compact readout circuits for SPAD arrays," 2010, Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium, pp.357-360

- [9] J.A Richardson. et al., "Scaleable Single-Photon Avalanche Diode Structures in Nanometer CMOS Technology," 2011, Electron Devices, IEEE Transactions on , vol.58, no.7, pp.2028-2035

- [10] W.J Marble and D.T.Comer, "Analysis of the dynamic behavior of a charge-transfer amplifier," 2010, Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on , vol.48, no.7, pp.793-804

- [11] E. Fossum, "The Quanta Image Sensor (QIS): Concepts and Challenges," 2011, Imaging Systems and Applications, OSA Technical Digest (CD) (Optical Society of America, 2011), paper JTuE1.s

Fig. 10. SCS Mode Pixel Sensitivity versus M8 V<sub>GS</sub>

Fig.12. SCS Mode Full Well Capacity versus M8 V<sub>GS</sub>

Fig. 11. SCS Mode PRNU versus M8 V<sub>GS</sub>

Fig. 13. SCS Mode Input Referred Noise versus M8  $V_{GS}$

Fig.14. Output Voltage Histograms For All Pixels at Varying Voltage Bias Under Constant Light